# DATA HANDBOOK

ICs for Telecom ISDN

**Philips Semiconductors**

**PHILIPS**

## ICs FOR TELECOM ISDN

|                           | page |

|---------------------------|------|

| Selection Guide           | , ,  |

| Functional index          | 5    |

| Numerical index           | , 7  |

| General                   |      |

| Type designation          | 11   |

| Product status definition | 13   |

| Rating systems            | 14   |

| Handling MOS devices      | 16   |

| Device data               | 17   |

| Package information       |      |

| Package outlines          | 279  |

| Soldering                 | 285  |

## SELECTION GUIDE

**Functional index**

**Numerical index**

## **FUNCTIONAL INDEX**

| type number                | description                                                                                                                                                                                              | page |  |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| DATA CONVERS               | SION                                                                                                                                                                                                     |      |  |  |  |  |

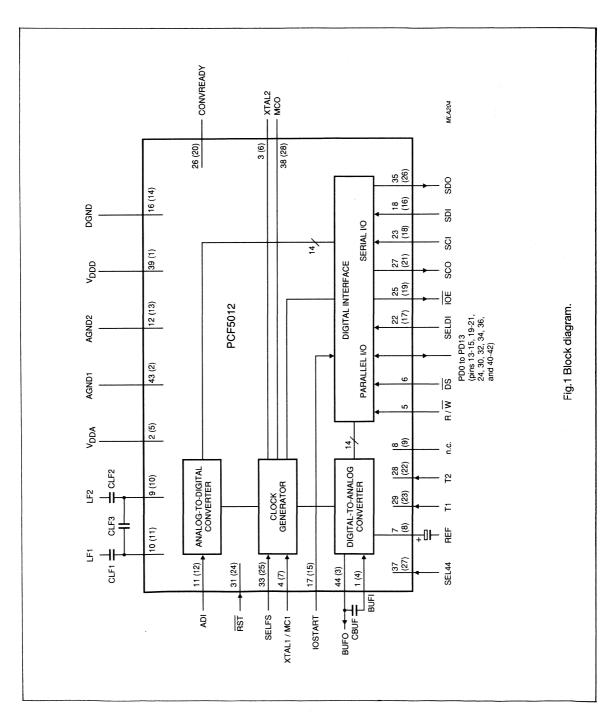

| PCF5012                    | 14-bit ADC/DAC; I <sup>2</sup> C-bus                                                                                                                                                                     | 241  |  |  |  |  |

| DATA RATE AD               | APTER                                                                                                                                                                                                    |      |  |  |  |  |

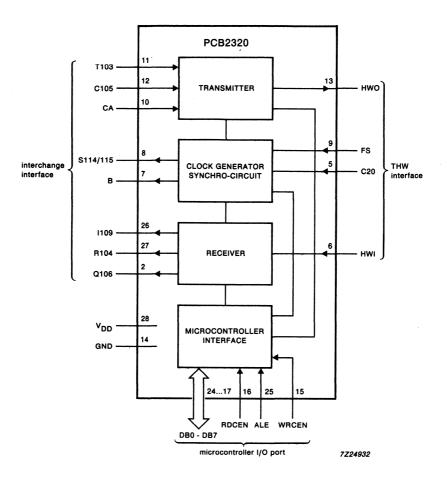

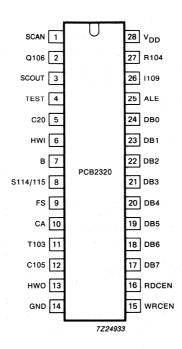

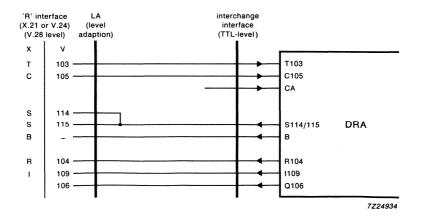

| PCB2320                    | data rate adapter (DRA)                                                                                                                                                                                  | 77   |  |  |  |  |

| PCB2325                    | extended data rate adapter                                                                                                                                                                               | 115  |  |  |  |  |

| DIGITAL SIGNA              | AL PROCESSORS                                                                                                                                                                                            |      |  |  |  |  |

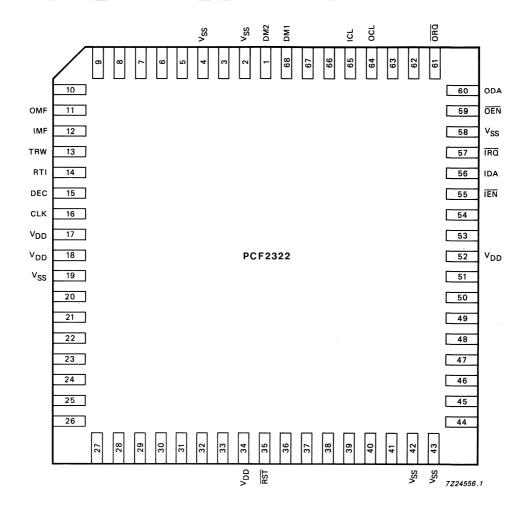

| PCF2322                    | wideband speech encoder/decoder                                                                                                                                                                          | 235  |  |  |  |  |

| I <sup>2</sup> C-BUS COMPA | TIBLE ICs                                                                                                                                                                                                |      |  |  |  |  |

| PCF5012                    | 14-bit ADC/DAC                                                                                                                                                                                           | 241  |  |  |  |  |

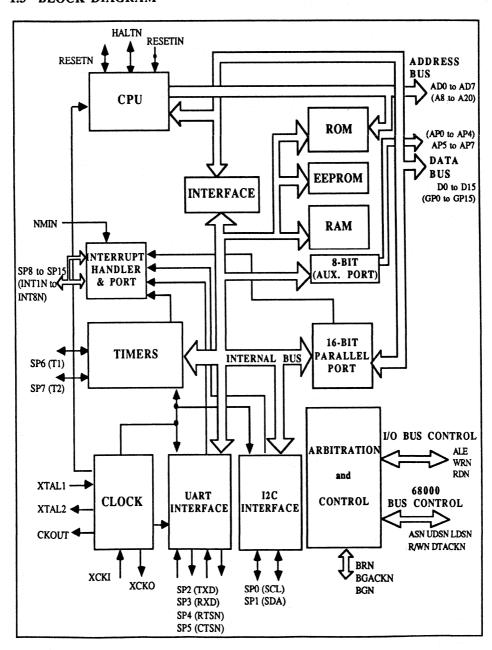

| 93C110                     | 16/32-bit microcontroller; 512 x 8 RAM; 34K x 8 ROM; 256 x 8 EEPROM; 40 I/O lines; UART; 16-bit counter/timer; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 15 MHz; 0 to + 70 °C | 225  |  |  |  |  |

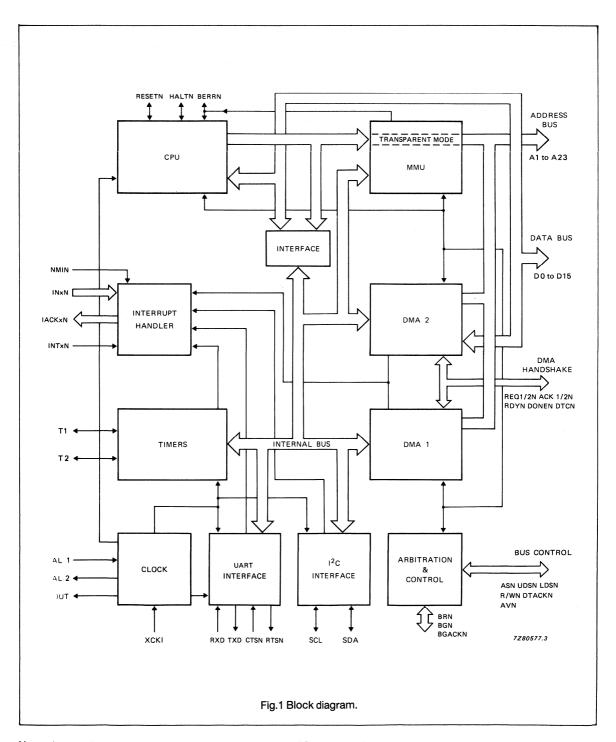

| SCC68070                   | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers                                              |      |  |  |  |  |

| IST BUS INTERI             | FACE                                                                                                                                                                                                     |      |  |  |  |  |

| PCB2310                    | IST-bus interface (IBI)                                                                                                                                                                                  | 37   |  |  |  |  |

| IST BUS SPECIFICATION      |                                                                                                                                                                                                          |      |  |  |  |  |

| MICROCONTRO                | OLLERS/PROCESSORS                                                                                                                                                                                        |      |  |  |  |  |

| 93C110                     | 16/32-bit microcontroller; 512 x 8 RAM; 34K x 8 ROM; 256 x 8 EEPROM; 40 I/O lines; UART; 16-bit counter/timer; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 15 MHz; 0 to + 70 °C | 225  |  |  |  |  |

| SCC68070                   | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus                        | 259  |  |  |  |  |

| SPEECH DECO                | DER                                                                                                                                                                                                      |      |  |  |  |  |

| PCF2322                    | Wideband speech encoder/decoder                                                                                                                                                                          | 235  |  |  |  |  |

## NUMERICAL INDEX

| type number   | description                                                                                                                                                                                                             | page                     |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|

| IST BUS       | integrated services terminal bus specification                                                                                                                                                                          | 19                       |  |  |  |

| PCB2310       | IST bus interface (IBI)                                                                                                                                                                                                 | 37                       |  |  |  |

| PCB2320       | data rate adapter (DRA)                                                                                                                                                                                                 | 77                       |  |  |  |

| PCB2325P      | extended data rate adapter                                                                                                                                                                                              | 115                      |  |  |  |

| PCB2325WP     | extended data rate adapter                                                                                                                                                                                              | 115                      |  |  |  |

| PCB93C110     | PCB93C110 16/32-bit microcontroller; 512 x 8 RAM; 34K x 8 ROM; 256 x 8 EEPROM; 40 I/O lines; UART; 16-bit counter/timer; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 15 MHz; 0 to + 70 °C      |                          |  |  |  |

| PCF2322WP     | wideband speech encoder/decoder                                                                                                                                                                                         | 235                      |  |  |  |

| PCF5012H      | 14-bit ADC/DAC; I <sup>2</sup> C-bus                                                                                                                                                                                    | 241                      |  |  |  |

| PCF5012P      | 14-bit ADC/DAC; I <sup>2</sup> C-bus                                                                                                                                                                                    | 241                      |  |  |  |

| PCF93C110     | 16/32-bit microcontroller; 512 x 8 RAM; 34K x 8 ROM; 256 x 8 EEPROM; 40 I/O lines; UART; 16-bit counter/timer; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 15 MHz; 0 to + 70 °C                | 225                      |  |  |  |

| SCC68070CBA84 | 259                                                                                                                                                                                                                     |                          |  |  |  |

| SCC68070CCA84 | 8070CCA84  16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 15 MHz; 0 to + 70 °C |                          |  |  |  |

| SCC68070CDA84 | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 17.5 MHz; 0 to + 70 °C          |                          |  |  |  |

| SCC68070ABA84 | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 12.5 MHz; -40 to + 85 °C        | 259                      |  |  |  |

| SCC68070ACA84 | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 15 MHz;40 to + 85 °C            | e; 16-bit timer/counter; |  |  |  |

# NUMERICAL INDEX

| type number                                                                                                                                                                                                                  | description                                                                                                                                                                                                      | page |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| SCC68070ADA84                                                                                                                                                                                                                | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 17.5 MHz; -40 to + 85 °C | 259  |  |  |

| SCC68070CBB                                                                                                                                                                                                                  | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 12.5 MHz; 0 to + 70 °C   | 259  |  |  |

| SCC68070CCB                                                                                                                                                                                                                  | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 15 MHz; 0 to + 70 °C     | 259  |  |  |

| SCC68070CDB                                                                                                                                                                                                                  | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 17.5 MHz; 0 to + 70 °C   | 259  |  |  |

| SCC68070ABB                                                                                                                                                                                                                  | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 12.5 MHz; —40 to + 85 °C | 259  |  |  |

| SCC68070ACB  16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter;  2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus;  0 to 15 MHz; -40 to +85 °C |                                                                                                                                                                                                                  |      |  |  |

| SCC68070ADB                                                                                                                                                                                                                  | 16/32-bit terminal microprocessor with MMU; 2-channel DMA controller; UART serial interface; 16-bit timer/counter; 2 x 16-bit match/count/capture registers; I <sup>2</sup> C-bus; 0 to 17.5 MHz; —40 to + 85 °C | 259  |  |  |

## **GENERAL**

Type designation Product status definition Rating systems Handling MOS devices

# Pro electron type designation code for integrated circuits

### TYPE DESIGNATION

#### Basic type number

This type designation applies to semiconductor monolithic, semiconductor multi-chip, thin film, thick-film and hybrid integrated circuits.

A basic type number consists of three letters followed by a serial number.

#### FIRST AND SECOND LETTER

#### **Digital family circuits**

The first two letters identify the family (see note 1).

#### **Solitary circuits**

The first letter divides the solitary circuits into:

S : solitary digital circuits

T: analog circuits

U: mixed analog/digital circuits

The second letter is a serial letter without any further significance except 'H' which stands for hybrid circuits (see note 2).

#### Microprocessors

The first two letters identify microprocessors and correlated circuits as follows:

MA: microcomputer

central processing unit

MB: slice processor (see note 3)

MD: correlated memories

ME: other correlated circuits (interface, clock, peripheral

controller, etc.)

#### Charge-transfer devices and switched capacitors.

The first two letters identify the following:

NH: hybrid circuits

NL: logic circuits

NM: memories

NS: analog signal processing, using switched capacitors

NT: analog signal processing, using change-transfer

device

NX: imaging devices

NY: other correlated circuits

#### THIRD LETTER

The third letter indicates the operating ambient temperature range. The letters A to G give information about the temperature:

A : temperature range not specified below (see note 4)

B : 0 to + 70 °C C : -55 to +125 °C D : -25 to + 70 °C E : -25 to + 85 °C F : -40 to + 85 °C G : -55 to + 85 °C

If a circuit is published for another temperature rang letter indicating a narrower temperature range may t used or the letter 'A'.

Example: the range 0 to +75 °C can be indicated by 'A'.

#### **SERIAL NUMBER**

This may be either a 4-digit number assigned by Prc Electron, or the serial number (which may be a combination of figures and letters) of an existing cor type designation of the manufacturer.

To the basic type number may be added:

#### Version letter(s)

A single version letter may be added to the basic type number. This indicates a minor variant of the basic type or the package. Except for 'Z', which means customized wiring, the letter has no fixed meaning. The following letters are recommended for package variants:

C : for cylindrical

D: for ceramic DIL

F : for flat pack (2 leads)G : for flat pack (4 leads)

H : for quadrature flat pack (OFP)

L : for chip on tape (foil)

P: for plastic DIL

Q: for QIL

T: for miniature plastic (mini-pack)

U: for uncased chip

# Pro electron type designation code for integrated circuits

### **TYPE DESIGNATION**

Alternatively a TWO LETTER SUFFIX may be used instead of a single package version letter, if the manufacturer (sponsor) wishes to give more information.

#### **FIRST LETTER: General shape**

C : cylindrical

D: dual-in-line (DIL)

E : power DIL (with external heatsink)

F : flat (leads on 2 sides)G : flat (leads on 4 sides)

H: quadrature flat pack (QFP)

K: diamond (TO-3 family)

M: multiple-in-line (except dual-, triple-, quadruple-

in-line)

Q: quadruple-in-line (QIL)

R : power QIL (with external heatsink)

S : single-in-lineT : triple-in-line

W : lead chip-carrier (LCC)X : leadless chip-carrier (LLCC)

Y : pin grid array (PGA)

#### **SECOND LETTER: Material**

C : metal-ceramic

G: glass-ceramic (cerdip)

M : metalP : plastic

To avoid confusion when the serial number ends with a letter, a hyphen is used preceding the suffix.

#### Examples (see note 5)

PCF1105WP : Digital IC, PC family, operational

temperature range -40 to +85 °C, serial number 1105, plastic leaded

chip-carrier.

GMB74LS00A-DC: Digital IC, GM family, operational

temperature range 0 to +70 °C, company number 74LSS00A, ceramic

DIL package.

TDA1000P : Analog circuit, no standard

temperature range, serial number

1000, plastic DIL package.

SAC2000 : Solitary digital circuit, operational

temperature range -55 to +125 °C.

#### **Notes**

- A logic family is an assembly of digital circuits designed to be interconnected and defined by its basic electrical characteristics (such as: supply voltage, power consumption, propagation delay, noise immunity).

- The first letter 'S' should be used for all solitary memories, to which, in the event of hybrids, the second letter 'H' should be added (e.g. SH for Bubblememories).

- By 'slice processor' is meant: a functional slice of microprocessor.

- In the case of two same types with two different temperature ranges not specified below, one type should use the letter 'A' as the third letter and the other, the letter 'X'.

- Some companies have been using version letters and/ or two letter-suffix, which differ from the Pro Electron definitions. In case of confusion Pro Electron may be contacted.

April 1990 12

#### **DEFINITIONS**

| Data sheet status         |                                                                                       |  |  |  |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |  |  |  |  |  |  |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |  |  |  |

| Product specification     | This data sheet contains final product specifications.                                |  |  |  |  |  |  |

| Limiting values           |                                                                                       |  |  |  |  |  |  |

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### **RATING SYSTEMS**

The rating systems described are those recommended by the International Electrotechnical Commission (IEC) in its Publication 134.

#### **DEFINITIONS OF TERMS USED**

Electronic device. An electronic tube or valve, transistor or other semiconductor device.

Note

This definition excludes inductors, capacitors, resistors and similar components.

Characteristic. A characteristic is an inherent and measurable property of a device. Such a property may be electrical, mechanical, thermal, hydraulic, electro-magnetic, or nuclear, and can be expressed as a value for stated or recognized conditions. A characteristic may also be a set of related values, usually shown in graphical form.

Bogey electronic device. An electronic device whose characteristics have the published nominal values for the type. A bogey electronic device for any particular application can be obtained by considering only those characteristics which are directly related to the application.

Rating. A value which establishes either a limiting capability or a limiting condition for an electronic device. It is determined for specified values of environment and operation, and may be stated in any suitable terms.

Note

Limiting conditions may be either maxima or minima.

Rating system. The set of principles upon which ratings are established and which determine their interpretation.

Note

The rating system indicates the division of responsibility between the device manufacturer and the circuit designer, with the object of ensuring that the working conditions do not exceed the ratings.

#### ABSOLUTE MAXIMUM RATING SYSTEM

Absolute maximum ratings are limiting values of operating and environmental conditions applicable to any electronic device of a specified type as defined by its published data, which should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in the characteristics of the device under consideration and of all other electronic devices in the equipment.

The equipment manufacturer should design so that, initially and throughout life, no absolute maximum value for the intended service is exceeded with any device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variations, signal variation, environmental conditions, and variations in characteristics of the device under consideration and of all other electronic devices in the equipment.

#### **DESIGN MAXIMUM RATING SYSTEM**

Design maximum ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking responsibility for the effects of changes in operating conditions due to variations in the characteristics of the electronic device under consideration.

The equipment manufacturer should design so that, initially and throughout life, no design maximum value for the intended service is exceeded with a bogey device under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, variation in characteristics of all other devices in the equipment, equipment control adjustment, load variation, signal variation and environmental conditions.

#### **DESIGN CENTRE RATING SYSTEM**

Design centre ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under normal conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device in average applications, taking responsibility for normal changes in operating conditions due to rated supply voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions, and variations in the characteristics of all electronic devices.

The equipment manufacturer should design so that, initially, no design centre value for the intended service is exceeded with a bogey electronic device in equipment operating at the stated normal supply voltage.

## HANDLING MOS DEVICES

#### HANDLING MOS DEVICES

Though all our MOS integrated circuits incorporate protection against electrostatic discharges, they can nevertheless be damaged by accidental over-voltages. In storing and handling them, the following precautions are recommended.

#### Caution

Testing or handling and mounting call for special attention to personal safety. Personnel handling MOS devices should normally be connected to ground via a resistor.

#### Storage and transport

Store and transport the circuits in their original packing. Alternatively, use may be made of a conductive material or special IC carrier that either short-circuits all leads or insulates them from external contact.

#### Testing or handling

Work on a conductive surface (e.g. metal table top) when testing the circuits or transferring them from one carrier to another. Electrically connect the person doing the testing or handling to the conductive surface, for example by a metal bracelet and a conductive cord or chain. Connect all testing and handling equipment to the same surface.

Signals should not be applied to the inputs while the device power supply is off. All unused input leads should be connected to either the supply voltage or ground.

#### Mounting

Mount MOS integrated circuits on printed circuit boards *after* all other components have been mounted. Take care that the circuits themselves, metal parts of the board, mounting tools, and the person doing the mounting are kept at the same electric (ground) potential. If it is impossible to ground the printed-circuit board the person mounting the circuits should touch the board before bringing MOS circuits into contact with it.

#### Soldering

Soldering iron tips, including those of low-voltage irons, or soldering baths should also be kept at the same potential as the MOS circuits and the board.

#### Static charges

Dress personnel in clothing of non-electrostatic material (no wool, silk or synthetic fibres). After the MOS circuits have been mounted on the board proper handling precautions should still be observed. Until the sub-assemblies are inserted into a complete system in which the proper voltages are supplied, the board is no more than an extension of the leads of the devices mounted on the board. To prevent static charges from being transmitted through the board wiring to the device it is recommended that conductive clips or conductive tape be put on the circuit board terminals.

#### Transient voltages

To prevent permanent damage due to transient voltages, do not insert or remove MOS devices, or printed-circuit boards with MOS devices, from test sockets or systems with power on.

#### Voltage surges

Beware of voltage surges due to switching electrical equipment on or off, relays and d.c. lines.

## DEVICE DATA

This data sheet contains advance information and specifications are subject to change without notice.

#### IST BUS SPECIFICATION

#### CONTENTS

#### 1.0 INTRODUCTION

#### 2.0 LAYER 1 CHARACTERISTICS

- 2.1 Configuration and definitions

- 2.2 Input impedance (Z<sub>I</sub>)

- 2.3 Line characteristics

- 2.4 Isolation

- 2.5 Line signal

- 2.6 Noise immunity

- 2.7 Receiver input sensitivity

- 2.8 Phantom power supply

- 2.9 Frame structure

- 2.10 Frame alignment

- 2.11 bd access protocol

- 2.12 b channel access protocol

#### 3.0 LAYER 2 PROTOCOL FOR THE bd CHANNEL

- 3.1 Service

- 3.2 Protocol

- 3.3 Maintenance

#### 4.0 LAYER 3 OF THE bd CHANNEL

#### 1.0 INTRODUCTION

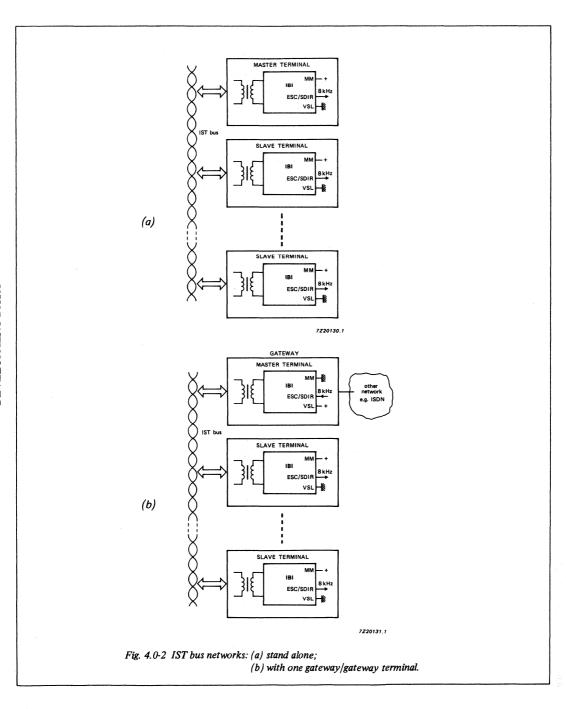

The Integrated Services Terminal (IST) bus offers a low cost in-house communication network. The voice service and the data service are integrated in one communication network,

As a stand alone digital communication network the IST bus provides in-house communication for up to 31 terminals within a range of 300 metres. Up to four terminals can converse simultaneously, while the exchange of data packets is allowed at the same time.

Interconnection of terminals is via a simple, easy to install, single twisted-pair cable. Terminals can be connected and disconnected at any time provided that the total number connected does not exceed 31. Only administration information should be kept on the identification number of a terminal

If a wider communication range is required it is possible to gate data paths via a "gateway" to other networks, especially a gateway to the ISDNS reference point (note 1). The 8 kHz synchronous frame of the IST bus could be synchronized in the gateway to an 8 kHz external source.

The protocol on the IST bus is completely distributed along the members of the bus. There is no central bus controller. This ensures a reliable bus system because even if a terminal fails the communication between others will not be disturbed.

The IST bus is mainly optimized for voice communication and offers eight 64 kbit/s circuit-switched channels (b1 to b8), time multiplexed on an 8 kHz frame structure. The protocol to access one of these channels is distributed along the terminals connected on the bus. Each terminal could access arbitrarily one or more of these circuit-switched channels. A 64 kbit/s packet-switched data channel (bd) is provided next to these eight circuit-switched channels. The bd channel is the IST equivalent of the ISDN "D" channel. The b1 to b8 channels are the IST equivalent of the ISDN "B" channels.

Layers 1 and 2 of the 7-layer hierarchy of the Open Systems Interconnection (OSI) model developed by the International Standardization Organization (ISO) built on this packet-switched channel are specified. Layer 2 offers a datagram service (note 2) with error free transmission of data packets and flow control. The access mechanism to this channel is the slotted CSMA/CD protocol (note 3). With this protocol access is guaranteed even with a 100% load. This makes the IST bus also suitable for process control.

The IBI, an IST Bus Interface (PCB2310) is a VLSI circuit which offers the complete protocols for the b channels and the protocol up to layer 2 for the data channel. The coupling to the bus will be achieved with a simple transformer.

#### Notes to the Introduction

- 1. The ISDN reference point has been specified by the CCITT in recommendations I430, I440 and I450.

- 2. A datagram service is a connectionless service specified by ISO; see also section 3.0.

- CSMA/CD is Carrier Sense Multiple Access with Collision Detection. If a collision occurs terminals are allowed to transmit only in specific time slots. See bd access mechanism.

#### 2.0 LAYER 1 CHARACTERISTICS

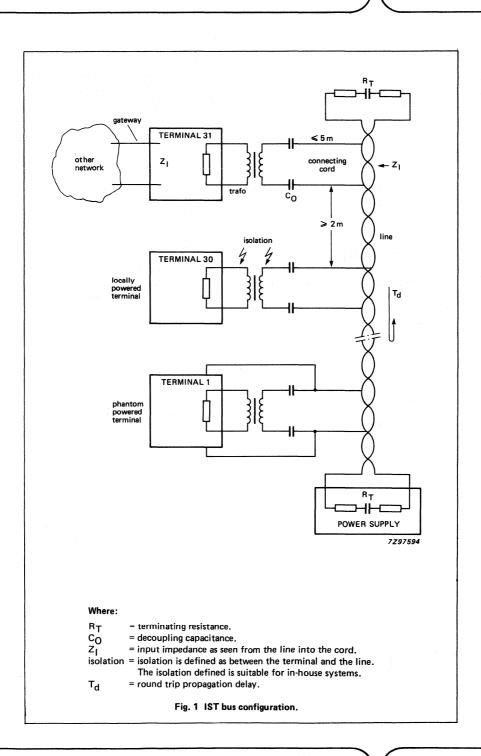

#### 2.1 Configuration and definitions

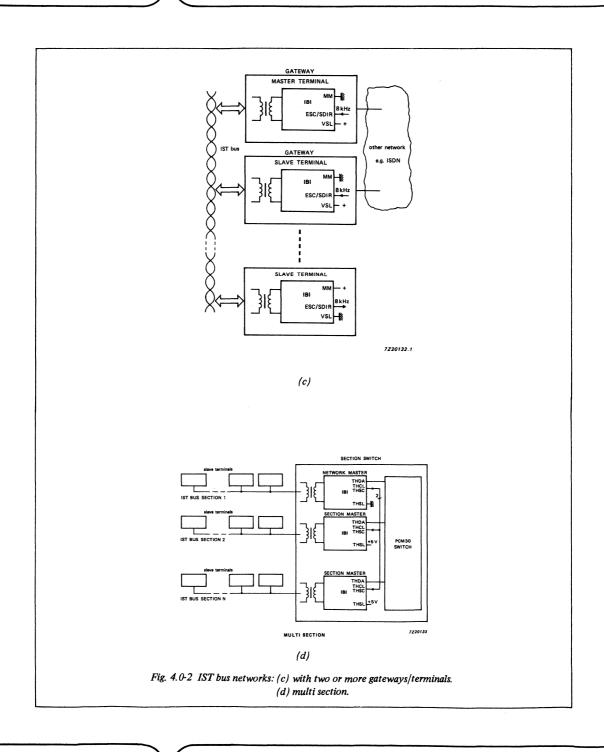

It is possible to connect up to 31 terminals on the IST bus. One or more terminals could have connections to other networks, these terminals are called gateways. A terminal could be any equipment with the facility to communicate digital information to other equipment. e.g.

digital voice communication : telephone, intercom

digital data communication : computers, printers,

telex, alarm indicators, slow scan television

Physically the interface of the IST bus is a twisted-pair cable leading to all terminals. A digital transmission technique is used for the transfer of data.

Logically the IST bus defines a set of protocols. These protocols specify the distribution of the transmission capability among the connected terminals.

The connection of terminals on the IST bus is limited by the distance between connected terminals being not less than 2 metres. Connection is achieved via a cord with a maximum length of 5 metres and a transformer. Each terminal must have a unique number between 1 and 31.

Because the IST bus is a twisted-pair cable and the voltage on the line is less then 1,25 V, pick-up and emission of radiated interference is minimal.

It is possible to distribute phantom power accross the interface using the same leads that are used for the data transmission due to the fact that the Alternative Mark Inversion (AMI) line code has been used. The voltage must be less than 42,5 V in accordance IEC safety regulations.

A configuration of the IST bus is shown in Fig. 1.

#### 2.2 Input impedance (Z<sub>I</sub>)

Because terminals are connected as stubs along the line the input impedance must be such that when 31 terminals are connected digital transmission are not disturbed.

The real part of the impedance should be such that if 31 terminals are located close together the reflections caused by these terminals are less than 10% at 500 kHz.

DC decoupling capacitors should be larger than  $1 \mu F$ .

#### 2.3 Line characteristics

A twisted pair of cables should be used. Characteristic impedance must be in the range:

$$Z_{\Omega} = 75 \text{ to } 150 \Omega$$

Correct matching of the line is achieved when the terminating resistance is:

$$R_T = Z_0 \pm 2\%$$

The round trip propagation delay must be:

$$T_{cl}$$

< 3000 ns

And the maximum attenuation is:

$$A = 20^{10} log V_{I}/V_{O} < 6 dB (f = 500 kHz)$$

#### 2.4 Isolation

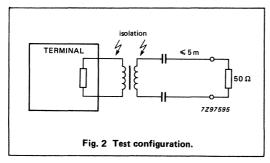

The isolation specified here is suitable for in-house systems.

A locally powered terminal must have a security isolation of more then 1500  $\rm V$ .

Terminals should withstand:

Common mode voltage surge with:

amplitude = 500 V rise time = 1  $\mu$ s fall time = 1000  $\mu$ s

The source impedance is 0,015  $\mu$ F

Differential mode voltage/current surge with:

amplitude = 50 V rise time = 1  $\mu$ s

fall time =  $50 \mu s$

The source impedance has a current limit of 200 mA

#### 2.5 Line signal

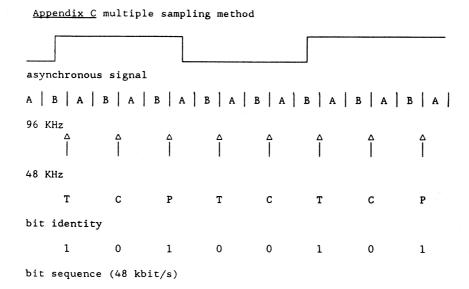

The line code is Alternative Mark Inversion. A logic 1 will result in a positive or a negative pulse on the line. A logic 0 will result in no signal on the line.

The nominal output voltage will be 1100 mV  $\pm$  150 mV into 50  $\Omega$  using the test configuration shown in Fig. 2.

The bit rate is 1,024 kbits/s  $\pm$  100 ppm; based on an 8,192 kHz  $\pm$  100 ppm crystal.

The difference between the positive and the negative pulse should be less than:

$$\int \frac{\text{positive pulse}}{\text{negative pulse}} dt < 5\%$$

#### 2.6 Noise immunity

The receiver must have a noise immunity to an input signal of  $70\,\text{mV}$  rms and below when f=0 to  $1\,\text{MHz}$ .

#### 2.7 Receiver input sensitivity

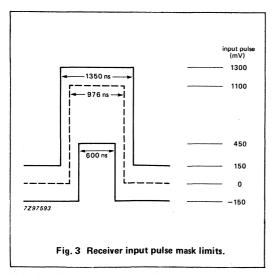

The receiver must handle input pulses as shown by the limits in Fig. 3. This also puts constraints on the transmitter output pulse.

#### 2.8 Phantom power supply

Because the power spectrum of the AMI line code is zero for DC it is possible to distribute phantom power over the signal lines. The power supply of 42,5 V (max.) should not disturb the IST bus. The power available at the terminal is 400 to 600 mW and a maximum of 5 to 10 terminals could be powered. Connecting a terminal to the IST bus could cause the system to go down for some milli seconds.

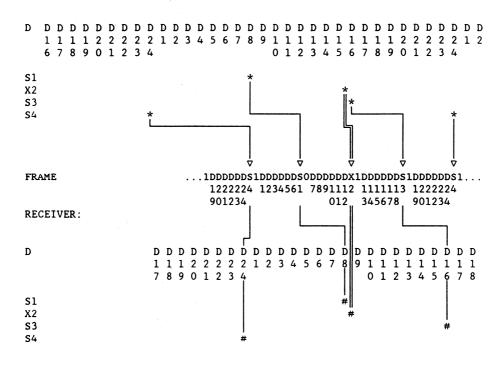

#### 2.9 Frame structure

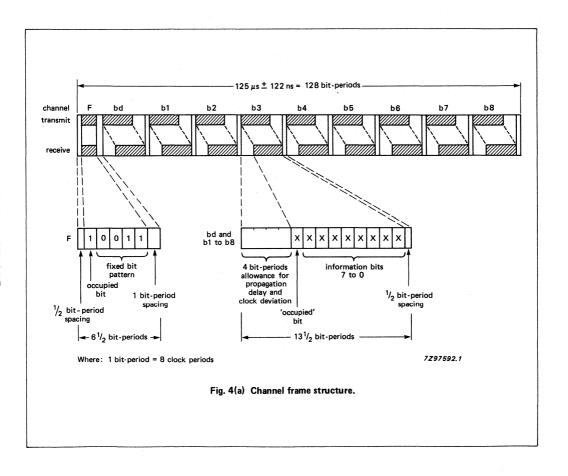

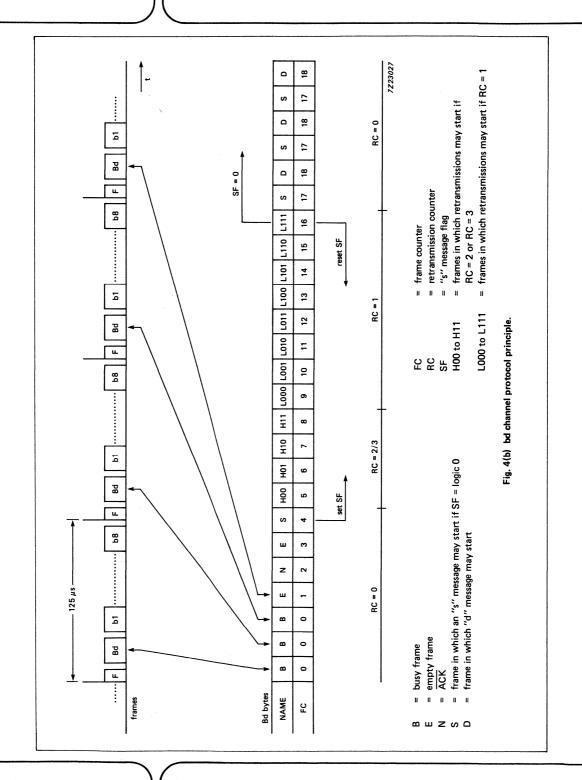

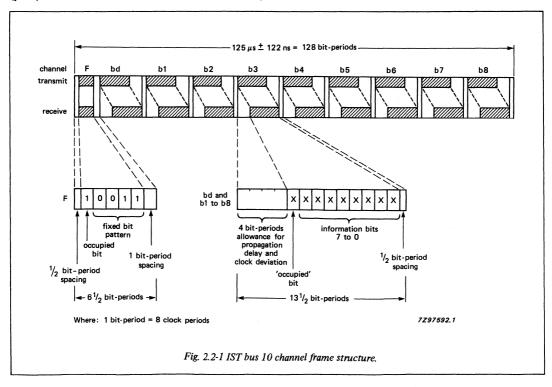

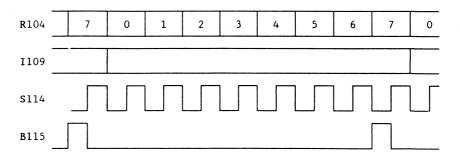

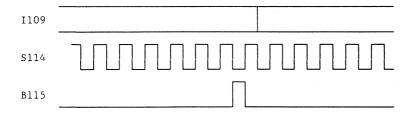

A frame of  $125 \mu s \pm 122 ns$  contains ten time division multiplexed channels as shown in Fig. 4:

1 x 32 kbit/s synchronization channel ; Frame (F)

1 x 64 kbit/s packet-switched channel ; Data (bd)

8 x 64 kbit/s circuit-switched channels ; Data/voice (b1 to b8)

Each channel is preceded by an occupied bit which is logic 1 if the channel is occupied (this will result in a positive or a negative line signal). Due to line delays and synchronization a  $4\mu$ s shift in the bd and b1 to b8 channels is allowed;  $0.5\mu$ s is used as channel separation.

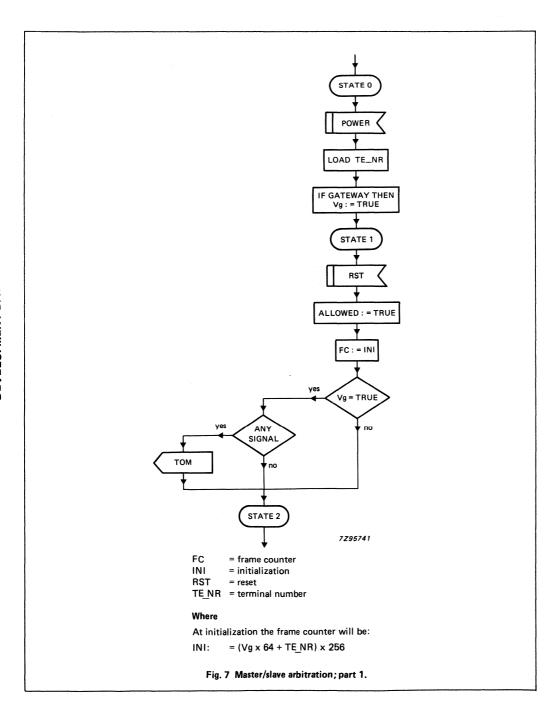

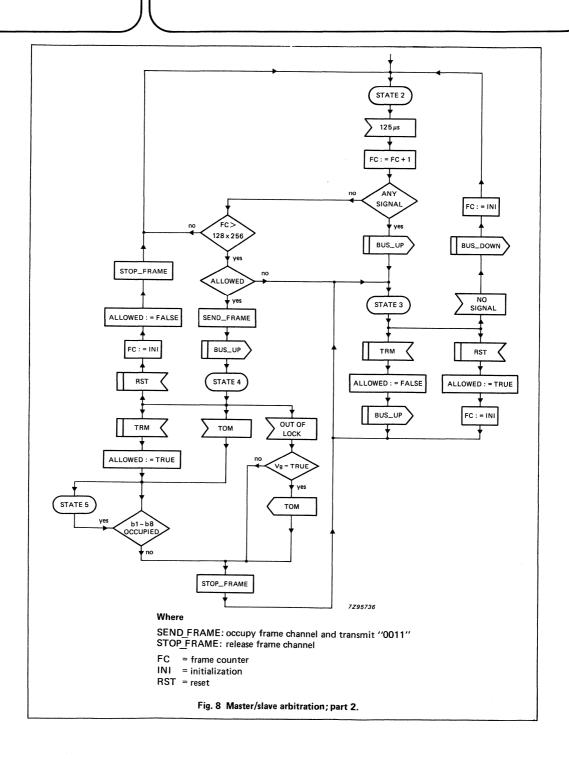

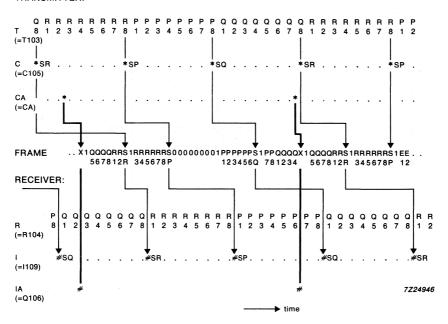

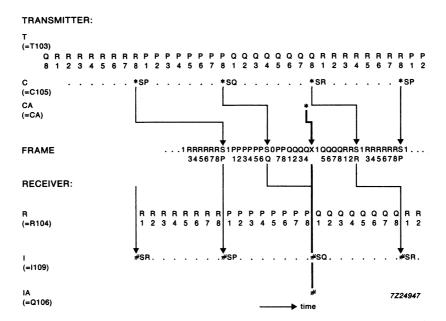

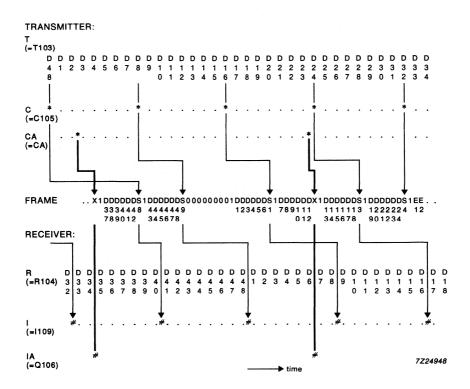

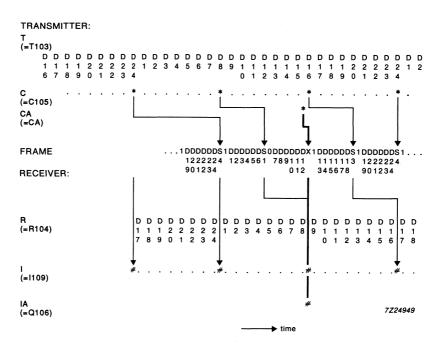

After power up one of the connected terminals should always transmit in the frame channel. The frame signal is coded "0011". The frame channel is used to synchronize all terminals to the 8 kHz frame. The terminal transmitting in the frame channel is the master and the others are the slaves. A fully distributed algorithm called master/slave arbitration determines which terminal will become the master. If a master fails another will automatically take over. One of the terminals connected to another network will always become the master of the IST bus. This terminal could be synchronized with that other network, but this can cause a jitter of 122 ns in the frame. The master/slave procedure is shown in Fig. 7 and Fig. 8.

If a gateway terminal connected to the IST bus is not master it will transmit a broadcast control message called "TOM". The current master will cease transmission in the frame channel as soon as all circuit-switched channels are free and the master/slave procedure restarts.

With a "TRM" primitive a terminal could request frame channel switch-off (after all circuit switched-channels are released) to enable terminal disconnection from the IST bus. A BUS\_DOWN, BUS\_UP primitive sequence (master) and a BUS\_UP primitive (slave) indicates that another terminal is the master of the IST bus.

#### 2.10 Frame alignment

A terminal should recognize the frame signal three consecutive frames before they are synchronized (in-lock). When a synchronized terminal fails to recognize the frame signal for three consecutive frames the terminal is unsynchronized again (out-of-lock). A terminal is only allowed to transmit in one of the bd and/or b1 to b8 channels when synchronized.

#### 2.11 bd access protocol

There are 3 types of message:

- "c" type; control message

- "d" type; data message

- "s" type; signalling message.

Access is determined such that terminals transmitting a "c" type or "s" type message have priority over terminals wanting to transmit "d" type messages. If a terminal has to transmit a "c" and an "s" type message the "c" type has priority. If a collision occurs between messages of the same type, the terminal number is decisive. Collided messages take priority over new messages to guarantee fair access. The terminal number is split into two parts to minimize access times. Table 1 illustrates the priority scheme.

Table 1 Access protocol priority scheme

| priority | message                        | terminal                      |

|----------|--------------------------------|-------------------------------|

| 1        | collided "c" or "s"            | high number<br>low number     |

| 2<br>3   | new "c" or "s"<br>collided "d" | <br>high number<br>low number |

| 4        | new "d"                        | - now number                  |

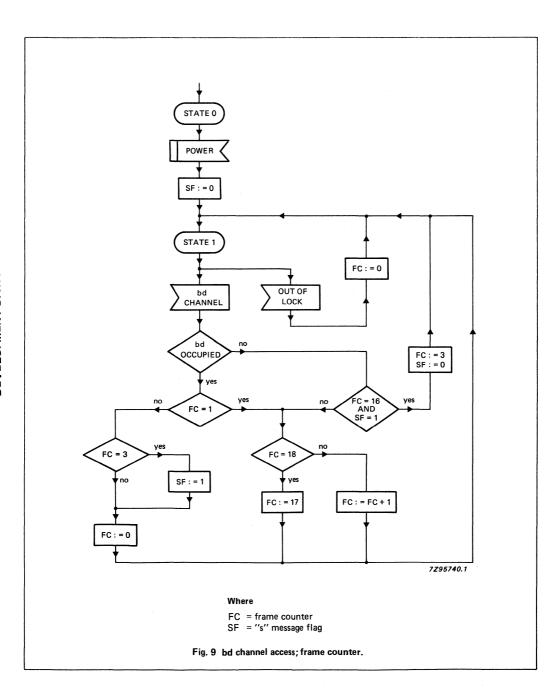

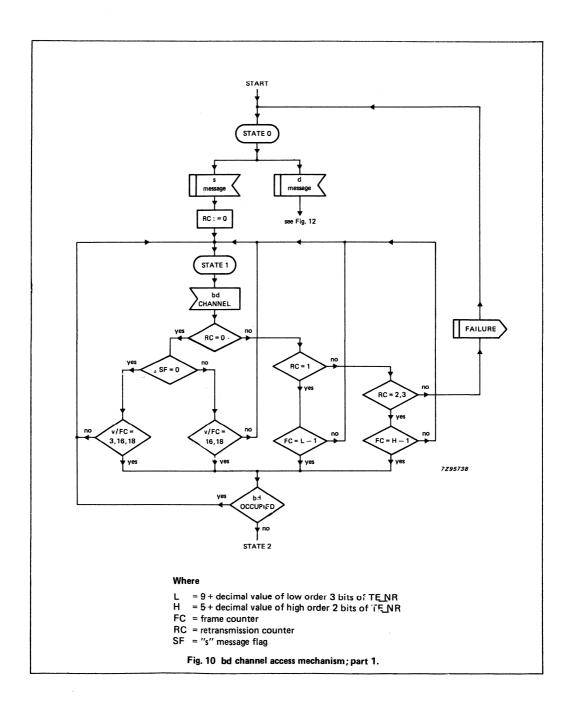

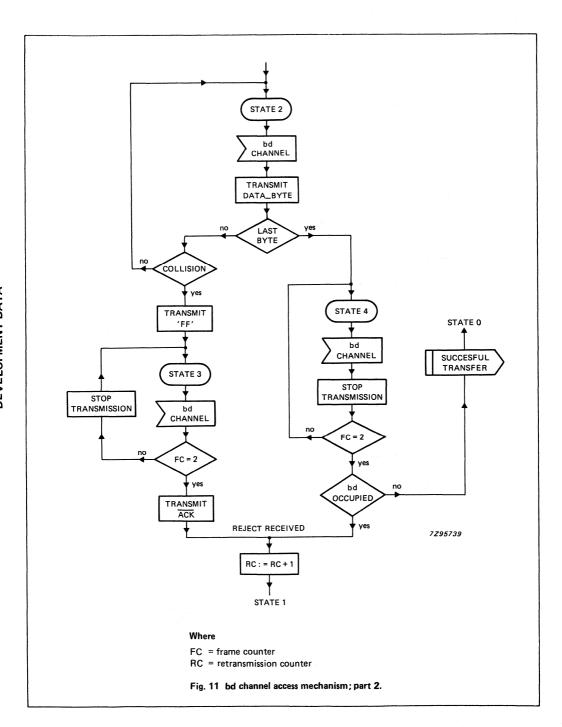

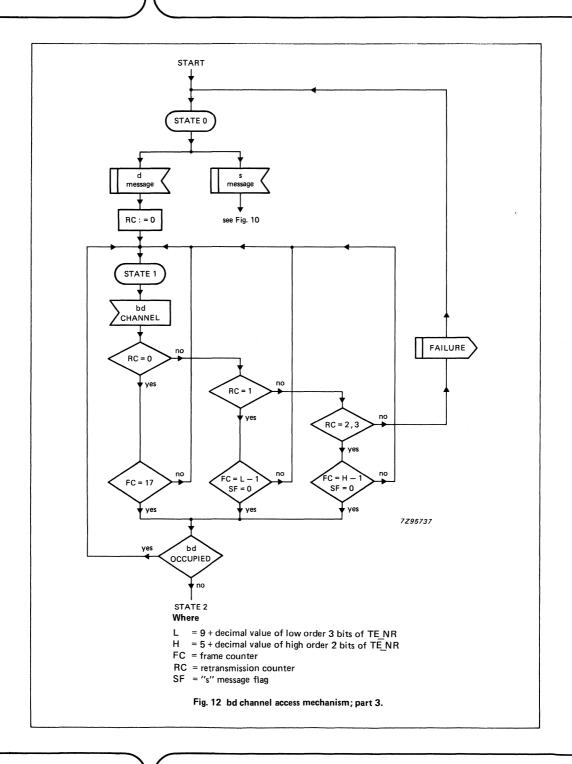

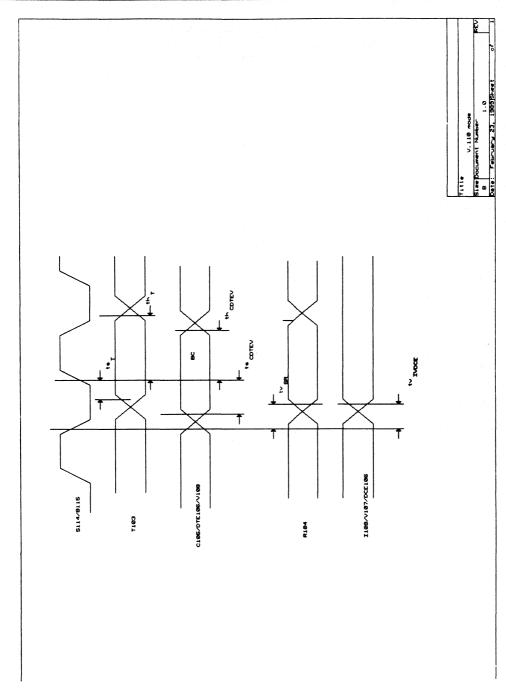

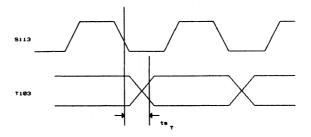

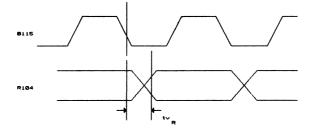

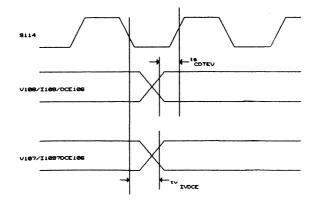

To access the bd channel the IST bus uses the CSMA/CD access protocol. The protocol of layer 2 for transmission of "s" and "d" messages is shown in the SDL diagrams, (Figs 9 to 12). The protocol treats "c" messages as "s" messages. In the IBI "s" and "c" messages have priority. The main part of the protocol is the bd channel access system and the frame-counter is closely related to this mechanism. Both of these mechanisms are illustrated in Fig.4(b).

Every IBI includes the frame-counter (FC) which is synchronized at the end of a packet transport in the bd channel whenever the bus is occupied. The frame indicated with B, E, N, S, H00 to H11, L000 to L111 and D have dedicated meanings as shown in Fig.4(b). The end of a packet transport is indicated by a frame in which the bd channel carries no start or information bits, i.e. an EMPTY frame (E). The frame that follows the E frame is the  $\overline{ACK}$  (N) frame. In this frame stations may transmit the not acknowledge code, 11111111. This code is used if retransmission is required due to transmission errors, collisions or destination receive buffers full. If the  $\overline{ACK}$  code is not needed the frame remains empty.

For circuit implementation reasons the N frame is followed by another E frame. After this first tine messages may access the bd channel in the S frame is SF = logic 0. SF is set to logic 1 if a transport is started in this frame. The 12 frames H00 to H11 and L000 to L111 are intended for retransmission purposes. In this field both signalling and data packets may start if SF = logic 0. If SF = logic 1 only signalling packets may access and data packets must wait for SF = logic 0 to occur.

If the ACK signal appears in the N frame the retransmission counters (RC) of the colliding terminals are increased. Depending on the 3 least significant bits of the 5 bit IST bus terminal address retransmissions will start in frames L000 to L111 when RC = 1. It is still possible that up to 4 stations can collide in this first retransmission period. Stations affected will start a second retransmission in the frames H00 to H11 (RC = 2) depending on the 2 most significant bits of the station's address. During the second retransmission period collisions cannot occur because the involved stations have different address bits.

Reception of  $\overline{ACK}$  however is still possible during this second retransmission period, occuring due to noise or inability of the buffer to accommodate the new packet, in order to distinguish between these 2 conditions the transmission is repeated once more in frames H00 to H11 (RC = 3). If after this  $\overline{ACK}$  is again received it is concluded that the receiving station was unable to store the packet. The transmitting chip will then warn its controller with a transmission overflow message. With the exception of frame control messages, (which only deal with layer 1), the transmitting chip confirms the transmission of all error free transfers with its controller.

The internal frame-counter is returned to the E position (FC = 3) in frame L111, if SF = logic 1 or access occurs during this frame, in order to give waiting data packets a retransmission chance. SF is reset at this time.

If during frame L111 SF = logic 0 and no access occurs, the internal frame-counters continue with S and D frames sequentially. First time signalling and data packets may start during these frames. This is also the normal access routine when the bd channel has been idle for some time. The S and D frames prevent collision between signalling and data packets.

#### 2.12 b channel access protocol

The b channel access protocol is fully decentralized. All members along the IST bus have the same algorithm. Each terminal is free to occupy any number of b channels provided they are not occupied by another terminal b channels are not in pairs. To determine which terminal is allowed to access a b channel the access mechanism of the bd channel is used. If a terminal want to access a free b channel, it transmits a unique broadcast control message in the bd channel. This control message is called "OCP". After a successful transfer the terminal is allowed to access the first free b channel. A b channel is free if the occupied bit of that channel is logic 0 for at least two consecutive frames directly after the control message has been correctly transferred.

The availability of "enquiry or call transfer" is made possible by ordering a terminal to occupy a b channel directly after that specific b channel has been released. A channel is seen released if its occupied bit is logic 0 for at least one frame.

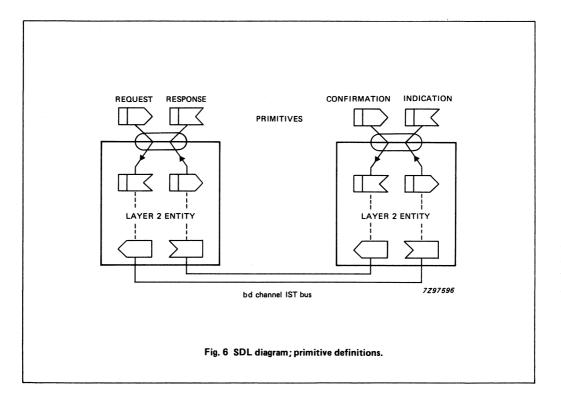

## 3.0 LAYER 2 PROTOCOL FOR THE bd CHANNEL

#### 3.1 Service

The service offered by the layer 2 protocol for the bd channel is a packet-switched datagram service. This means it is not necessary to set up a logical link before being able to transfer data packets. Layer 3 data is transferred transparantly by the layer 2 service. Two types of data packets can be transferred:

- "s" type packets for control of circuit-switched channels

- "d" type packets for data packet exchange between terminals

The average transfer delay of "s" types packets is less than that of "d" type packets due to the bd access protocol. The layer 2 message is controlled with a Cyclic Redundancy Check (CRC). If a message is received wrongly it will be retransmitted. Thus an error-free packet transmission can be guaranteed on an erroneous channel. Flow control is possible because a receiver can reject a data packet.

#### 3.2 Protocol

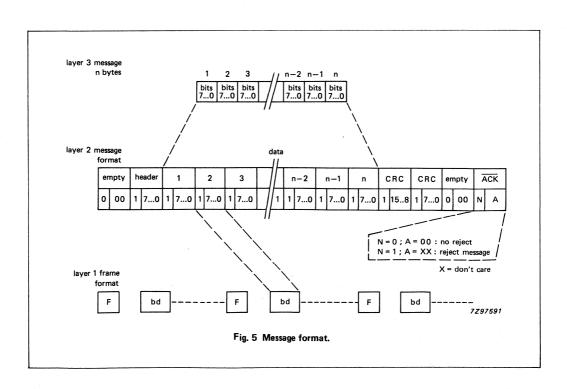

Packets are separated by at least one empty byte. An occupied bit at logic 0 in the bd channel indicates an empty byte. In the packet the occupied bit is set to logic 1 to ensure transparency as shown in Fig. 5.

Each packet will be immediately rejected two frames after the transmission if:

the calculated CRC in the receiver differs from the received CRC

or

a receiver is not able to receive the message because of pending messages

If a packet is rejected a not acknowledge (ACK) will be transferred immediately after the message.

The transmitter will then re-transmit its message in accordance with the bd access protocol. A rejection instead of an acknowledgement has been choosen because broadcast messages can be similarly rejected ("wired NOR"). However, a transmitter cannot detect whether a non-existing or a non-responding terminal has been addressed.

The trailer contains the 16-bit CRC. The CRC operation is a division of the complete layer 2 packet including the header. The divider is:

$$X^{16} + X^{12} + X^{5} + 1$$

and the initial remainder is "00".

The final remainder of the division will be transmitted in the two CRC bytes.

The header distinguishes the three types of messages:

- "c" or control type used for control over the frame and b channels

- "d" type which can transfer any kind of data

- · "s" signalling type used for routing etc.

The "s" and "d" type messages can address any specified terminal or all terminals (broadcast message). The "c" type messages address all terminals. Table 2 displays an overview of the bits in the header.

#### 3.3 Maintenance

Five control messages are used on the IST bus:

- The "OCP" message is used to control the b channel access and is unique for each terminal because of the terminal number in the header

- The "TOM" message is used to control the frame channel (see master/slave arbitration)

- The "AFS", "SAS" and the "SCO" messages are used to control the external synchronization procedures (see Figs 12 and 13)

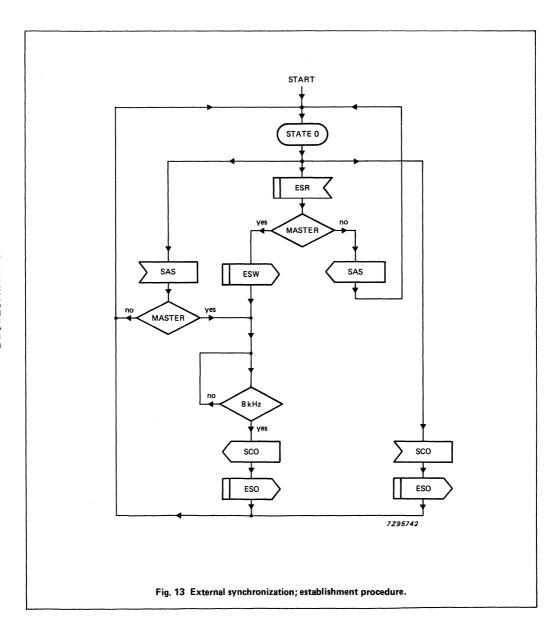

If a terminal wants to communicate to another network via a gateway it can ask the IST bus to synchronize with the external 8kHz source of that network. This procedure is initiated by an EXTERNAL\_SYNC\_REQUEST (ESR) primitive. If the terminal is not the master on the IST bus it will transmit an "SAS" control message in the bd channel. The gateway terminal will receive an EXTERNAL\_SYNC WANTED (ESW) upon receipt of an "SAS" message. If the external synchronization is established the "SCO" control message will be transferred to the bd channel and when received an EXTERNAL\_SYNC\_IS\_ON (ESO) primitive is given.

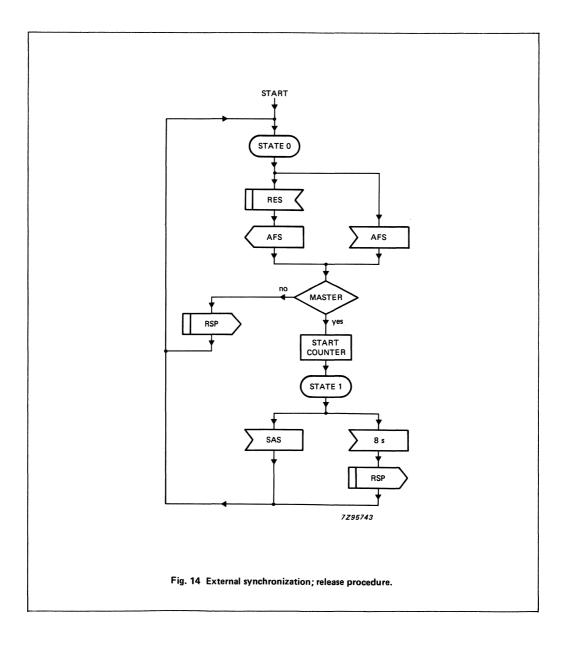

If the gateway wants to cease the external synchronization it issues an EXTERNAL\_SYNC\_RELEASE\_REQUEST (RES); the "AFS" control message is transferred and all terminals will receive an RELEASE\_EXTERNAL\_SYNC\_PROCEEDS (RSP). If there is no reaction within 8 seconds from other members on the IST bus the master releases the external synchronization.

The following other maintenance services are offered to the layer 3:

- If there is no signal on the IST bus a BUS\_DOWN\_ INDICATION (TMP) primitive is given

- When a signal reappears on the IST bus a BUS\_UP\_ INDICATION (TMF) primitive is given

- If the transfer of an "s" or "d" type message is failed an s\_FAILURE\_INDICATION (FAILURE) or a d\_FAILURE INDICATION (FAILURE) is given

A transfer is failed if a reject is still received after 3 retransmissions.

If a transfer is successful an s\_SUCCESS\_INDICATION (SUCCESSFUL) or a d\_SUCCESS\_INDICATION (SUCCESSFUL) primitive is given.

|                     | bit |   |   |                    |                      |      |      |      | type                                   |                                                 |

|---------------------|-----|---|---|--------------------|----------------------|------|------|------|----------------------------------------|-------------------------------------------------|

|                     | 7   | 6 | 5 | 4                  | 3                    | 2    | 1    | 0    |                                        |                                                 |

| control messages    | 1   | 1 | х | terminal number(n) |                      |      | r(n) | ОСР  | (occupation of b-channel will proceed) |                                                 |

| zero data bits      |     | 0 | 0 | 0                  | 0                    | 0    | 0    | 1    | TOM                                    | (transfer of master request)                    |

|                     |     |   |   | 0                  | 0                    | 0    | 1    | 0    | AFS                                    | (ask/give permission to finish synchronization) |

|                     |     |   |   | 0                  | 0                    | 0    | 1    | 1    | SAS                                    | (slave asks for synchronization)                |

|                     |     |   |   | 0                  | 0                    | 1    | 0    | 0    | SCO                                    | (synchronization is ON)                         |

| signalling messages | 0   | 1 | Х | des                | destination address* |      | "s"  |      |                                        |                                                 |

| data messages       | 0   | 0 | Х | des                | stina                | tion | addr | ess* | "d"                                    |                                                 |

#### Where:

X = don't care

Table 2 Header format

<sup>=</sup> all zeros indicate the broadcast address

### 4.0 LAYER 3 OF THE bd CHANNEL

To be specified.

PCB2310

This data sheet contains advance information and specifications are subject to change without notice.

# IST BUS INTERFACE (IBI)

## HOW TO USE THIS DATA SHEET

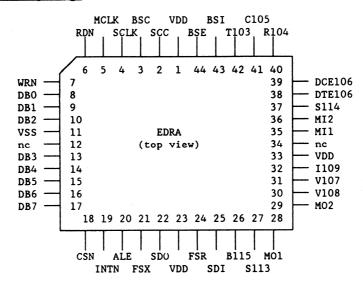

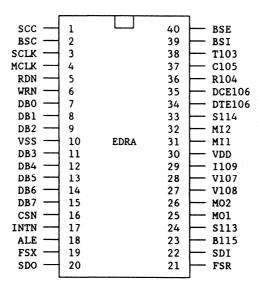

- Section 1 introduces the IST bus interface. The functional areas of the circuit are shown with a block diagram and all input and output signals are described. The physical locations of the signals are indicated in a pinning diagram. Ordering information is found in this section.

- Section 2 describes the functioning of the IST bus interface and follows the functional areas established by the block diagram in section 1. This section also describes how the functional areas are controlled by programmed instructions,

- Section 3 provides the electrical characteristics. This section is used when designing system hardware.

- Section 4 provides application information.

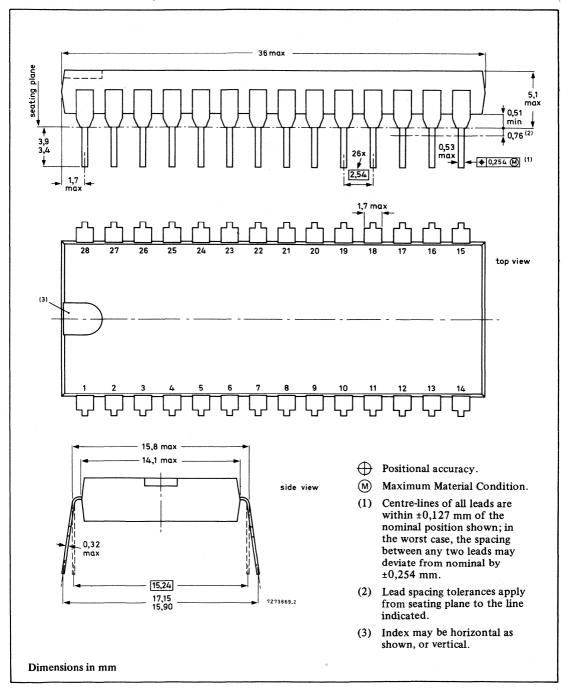

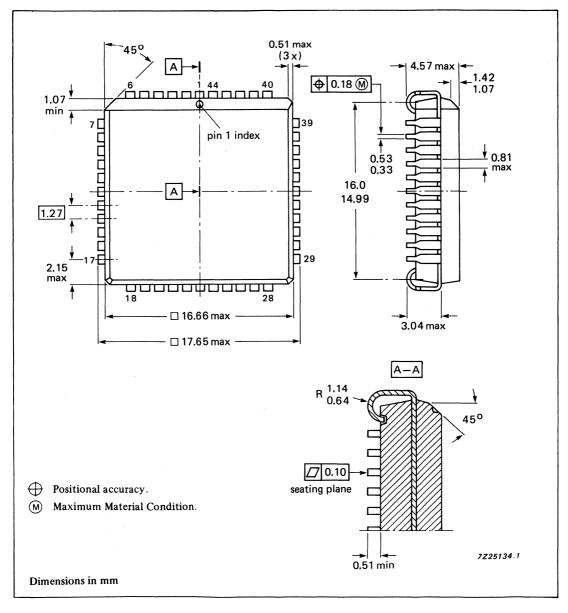

- Section 5 gives details of the PCB2310 packaging.

## **CONTENTS**

#### 1.0 INTRODUCTION

- 1.1 Features

- 1.2 Ordering information

- 1.3 Signal description

## 2.0 FUNCTIONAL DESCRIPTION

- 2.1 General description

- 2.2 IST bus description

- 2.2.1 bd channel

- 2.2.2 b channels

- 2.2.3 Frame channel

- 2.3 IST bus I/O stage

- 2.4 Terminal Highway interface

- 2.5 SLD bus interface/time slot assignment outputs

- 2.5.1 TSA mode

- 2.5.2 SLD mode

- 2.5.3 Combined TSA and SLD mode

- 2.5.4 Master mode

- 2.5.5 Slave mode

- 2.6 8-bit microcontroller bus

- 2.6.1 Registers P80, P81

- 2.6.1.1 Polling mode

- 2.6.1.2 Interrupt

- 2.6.2 Register P82; FIFO data path

- 2.7 Command description

- 2.7.1 Internal RAM/register read/write access

- 2.7.2 Registers

- 2.7.3 Reset command

- 2.7.4 bd channel interface primitives

- 2.7.5 SLD channel control

- 2.7.6 Circuit-switched channel control IST b1 to b8

- 2.7.7 IST master-slave/maintenance commands

- 2.7.8 External synchronization procedures

- 2.8 bd channel protocol

- 2.8.1 bd channel access protocol

- 2.9 Reset

- 2.10 Monitor mode

- 2.11 Crystal connection circuit

# 3.0 ELECTRICAL SPECIFICATION

- 3.1 Ratings

- 3.2 DC characteristics

- 3.2.1 Capacitance

- 3.3 AC characteristics

- 3.3.1 Timing

- 3.4 AC testing

#### 4.0 APPLICATION INFORMATION

## 5.0 PACKAGE OUTLINE

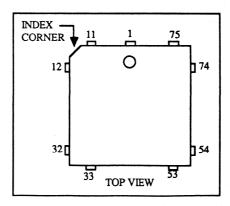

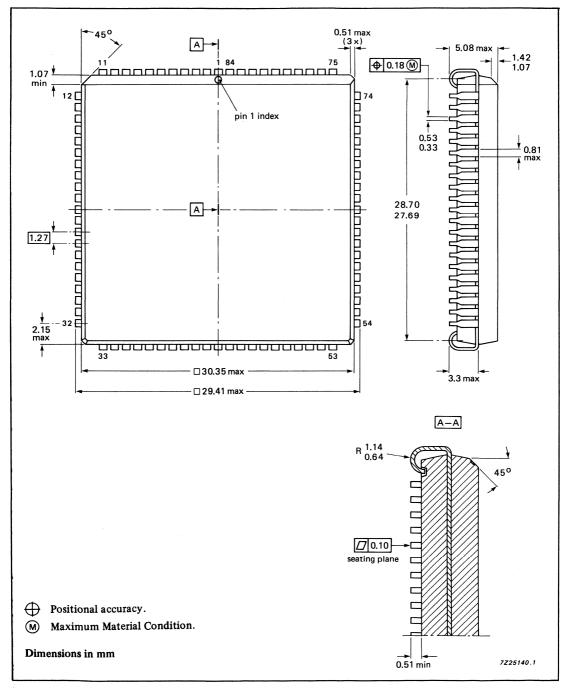

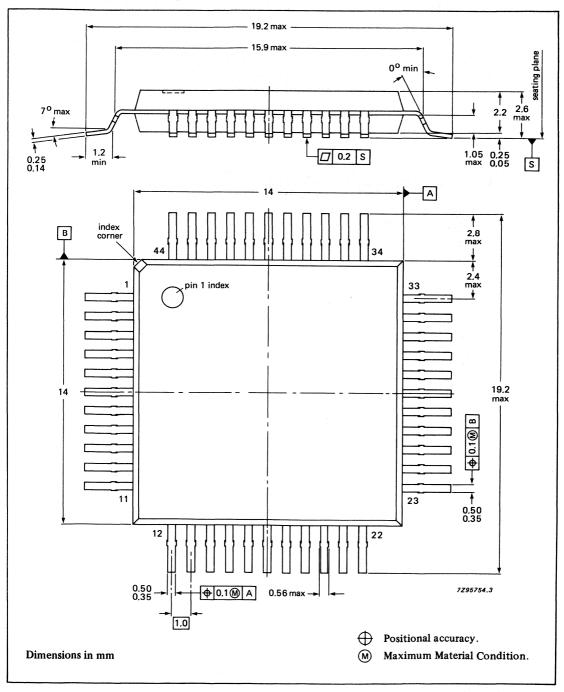

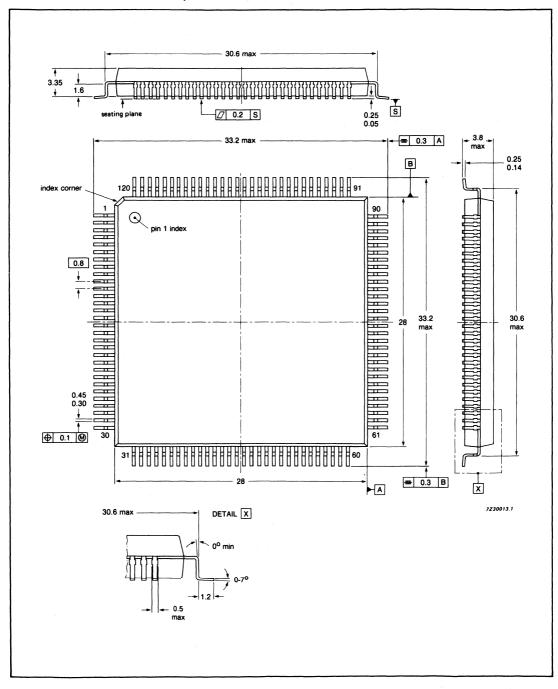

5.1 44-lead PLCC

#### 1.0 INTRODUCTION

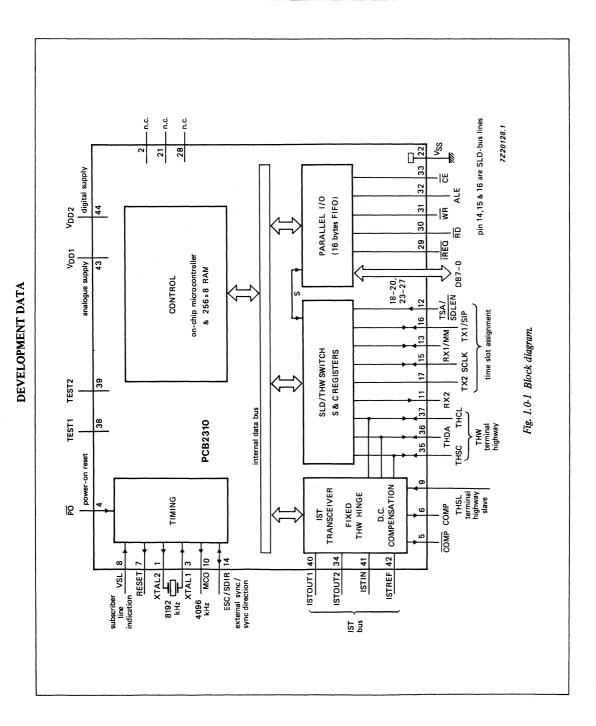

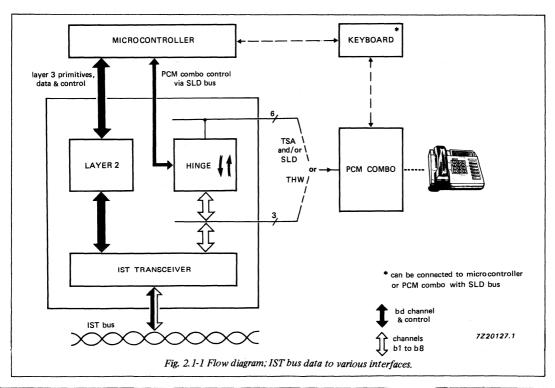

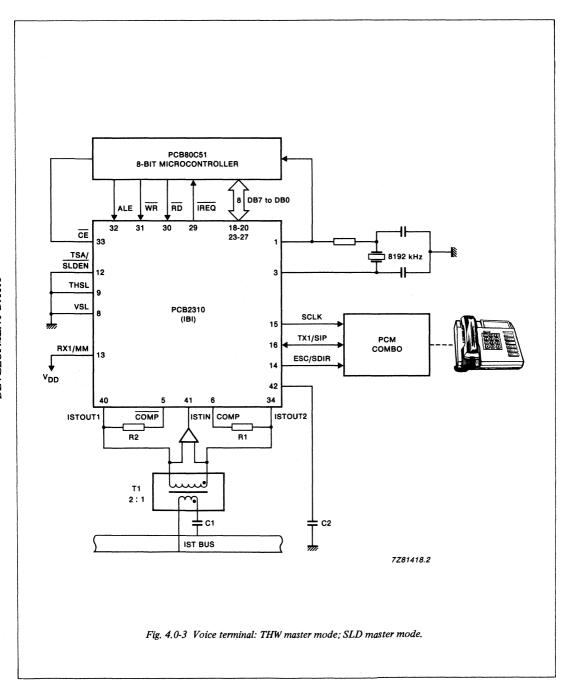

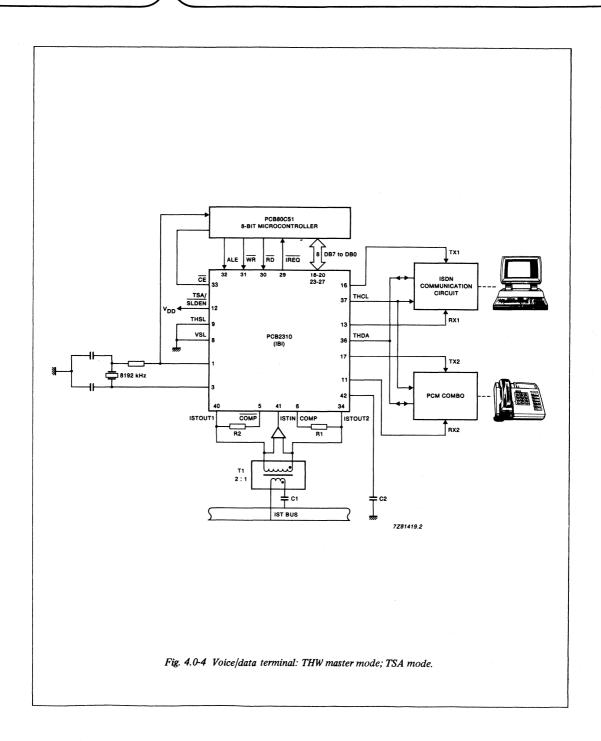

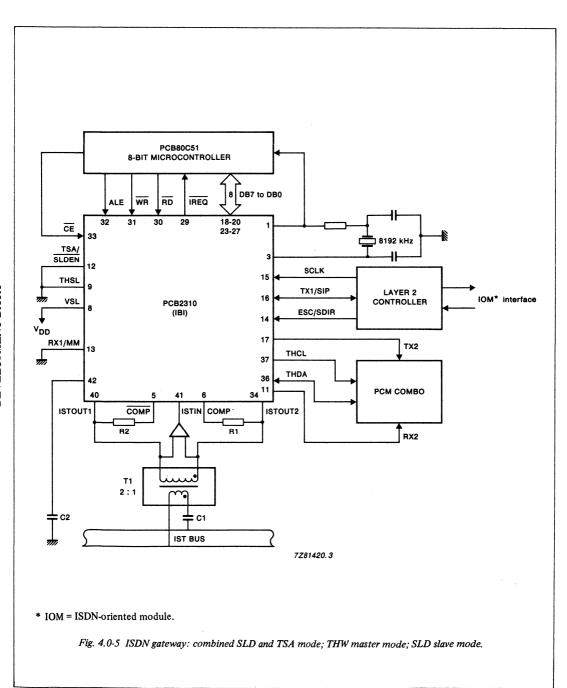

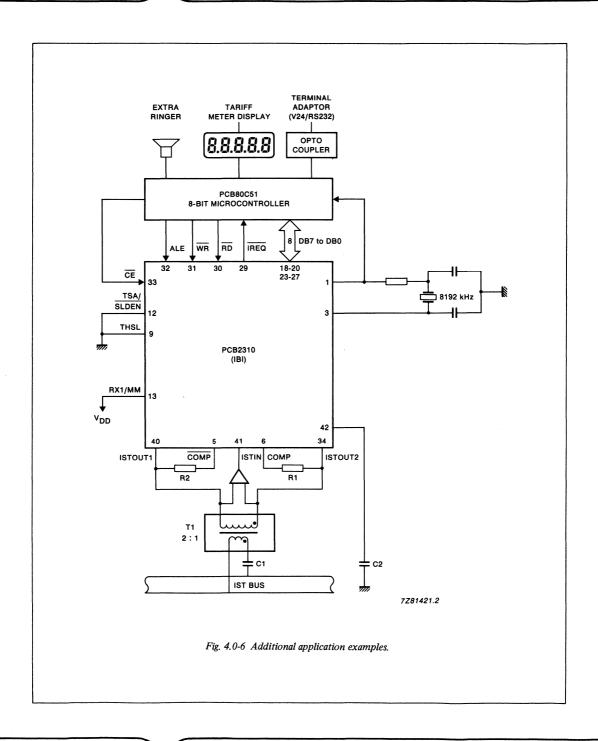

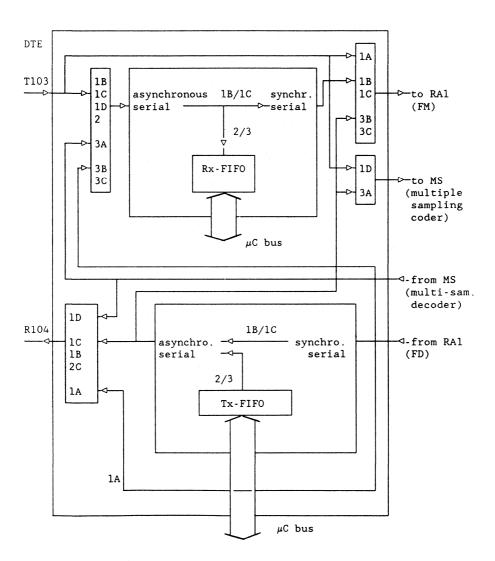

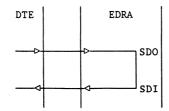

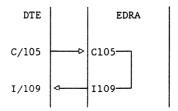

The PCB2310 is a CMOS integrated VLSI circuit offering a full layer 1 and 2 interface for the IST bus. It operates as the interface between the IST bus at one side and at the other side it interfaces to intra terminal interfaces such as Terminal Highway (THW), Subscriber Line Data (SLD) bus and an 8-bit microcontroller with multiplexed address/data I/O lines.

The PCB2310 is one of a set of circuits required to complete the modular terminal architecture for Integrated Services Digital Network (ISDN) terminals. For contemporary analogue telephone functions the PCB2310 in conjunction with a signal processing codec filter requires only a microcontroller, a power supply, a transformer and some discrete components.

The IBI is an interface between different buses namely:

- The IST bus is a Local Area Network (LAN) with a maximum length of 300 metres (see IST bus specification). It offers a low-cost local communication medium for voice and data communications and is compatible with the ISDN according to CCITT-I series of recommendations. The IST bus can also be used with current analogue and digital networks.

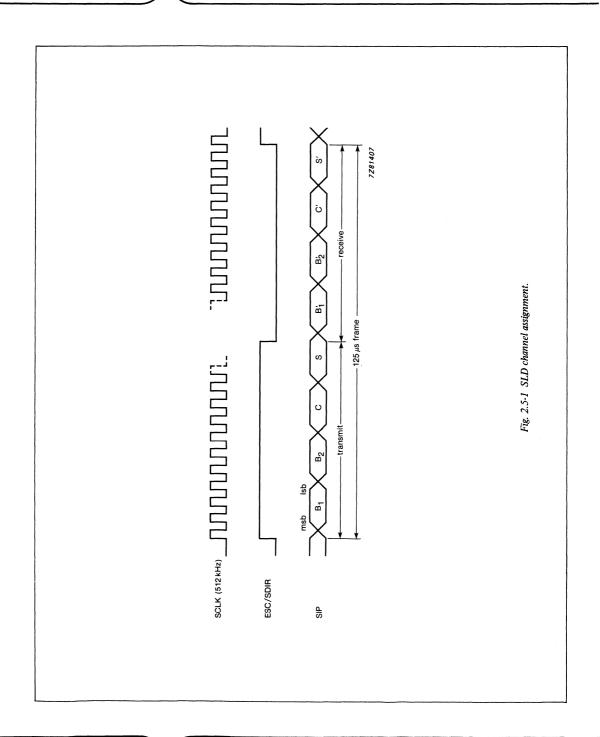

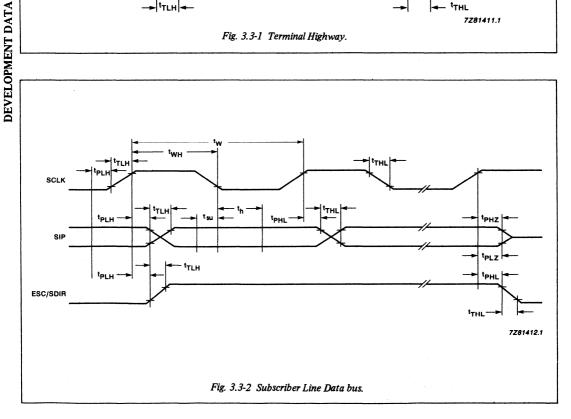

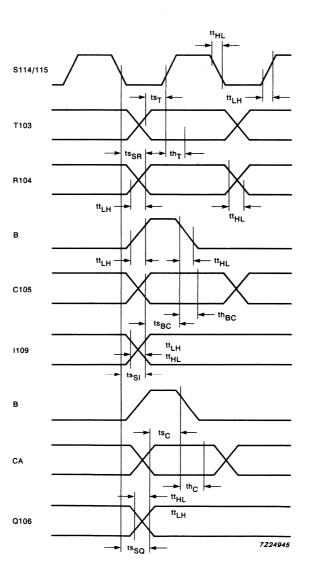

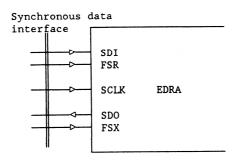

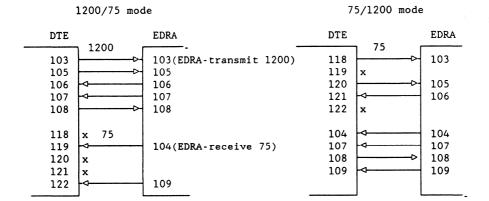

- The SLD bus is a standardized 8 kHz synchronous communication bus for on-board routing of B, S and C channels. The C (control) and S (signalling) channels of the SLD bus are accessed via the microcontroller I/O port.

- The 8-bit microcontroller is a PCB80C51 compatible microcontroller bus. The data and address lines are multiplexed.

- The THW is a PCM highway with a transmission rate of 2.048 Mbit/s.

The eight 64 kbit/s circuit-switched IST bus channels are mapped on time slots on the THW which can be switched to the two B channels of the SLD bus. The 64 kbit/s packet-switched channel is routed to the 8-bit microcontroller parallel I/O port. The PCB2310 offers layer 1 and 2 services of the 7-layer hierarchy of the Open Systems Inter-connection (OSI) model developed by the International Standardization Organization (ISO) in this packet-switched channel of the IST bus.

Table 2.6-6 gives a quick reference to the PCB2310.

#### 1.1 Features

- Designed to interface with a twisted-pair cable via a coupling transformer for galvanic isolation and/or d.c. supply

- On-chip 8192 kHz clock generator

- 8 kHz synchronous frame

- External 8 kHz synchronization input for gateways

- Alternative Mark Inversion (AMI) line code

- Receiver input phase locked to the IST bus frame

- Automatic frame word transmitter allocation

- Eight 64 kbit/s half duplex circuit-switched channels which are fixed mapped on time slots of the Terminal Highway (THW)

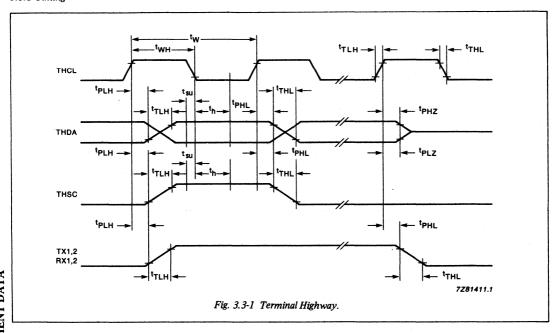

- Three-wire 2 Mbit/s 32-channel Terminal Highway (THW):

- THDA: Terminal Highway data I/O 3-state pin

THCL: Terminal Highway clock 2048 kHz clock

input/output

- THSC: Terminal Highway synchronization 8 kHz

- input/output

- 4096 kHz and 8192 kHz clock output

- Three-wire 512 kbit/s 8-channel SLD bus: SIP : SLD data I/O 3-state pin

- SCLK: SLD clock input/output pin ESC/SDIR: 8 kHz synchronization input/output

- On-chip B channel switches and interface for SLD bus

- Time slot assignment control for the two B channels

- Distributed collision-free circuit-switched channel access mechanism, no central controller required

- Circuit-switched channel transfer facility for register recall services on duplex links

- One half duplex 64 kbit/s packet-switched common signalling and data channel (bd) with the following features:

full layer 1 and 2 interface (OSI)

single frame protocol

immediate packet acknowledgement

100% guaranteed channel access based on CSMA/CD (Carrier Sense Multiple Access/with Collision Detection) layer 2 service offers error-free packet transmission; transmission errors are recovered by re-transmissions error detection based on Frame Check Sequence (FCS) using Cyclic Redundancy Check (CRC) divider. The divider is:

$$X^{16} + X^{12} + X^{5} + 1$$

and the initial remainder is '00' separate program-sized transmit and receive buffers for signalling (s) packets and data (d) packets signalling packets have transmission priority over data packets

flow control based on buffer availability

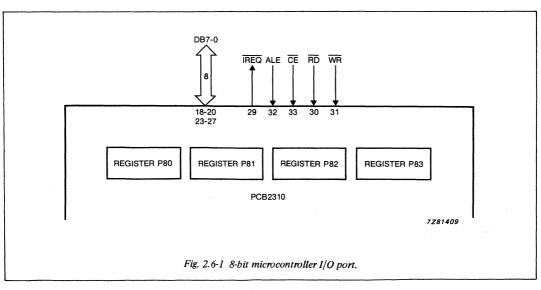

- 8-bit microcontroller I/O port including a 16-byte FIFO

- Access to S and C channels of SLD bus via 8-bit I/O port

- Maskable interrupt requests

- 21 control commands

- 13 control indications

- On-chip power-on reset circuit

- Monitor mode for bd channel

- Separate + 5 V supplies for analogue and digital parts

#### 1.2 Ordering information

| TYPE NUMBER | TEMPERATURE<br>RANGE °C | PACKAGE     |

|-------------|-------------------------|-------------|

| PCB2310WP   | 0 to +70                | 44-pin PLCC |

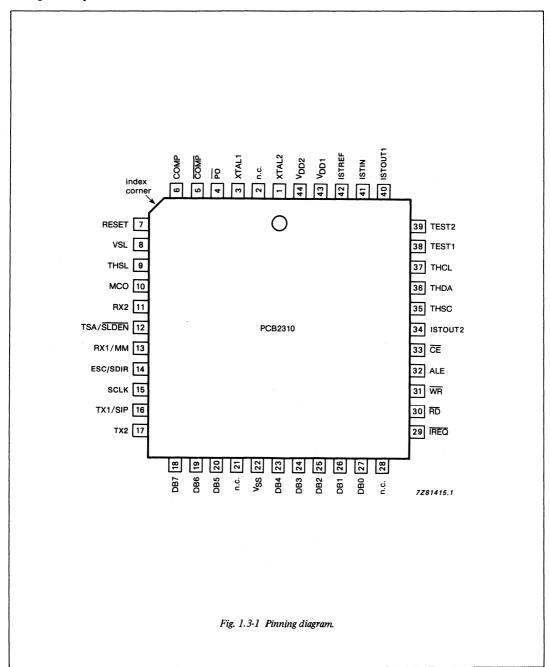

# 1.3 Signal description

DEVELOPMENT DATA

All inputs except  $\overline{PO}$  are TTL compatible. Unless otherwise specified all outputs can drive 2 TTL (= 8 LSTTL) inputs and equivalent CMOS inputs.

- 2 n.c. not connected.

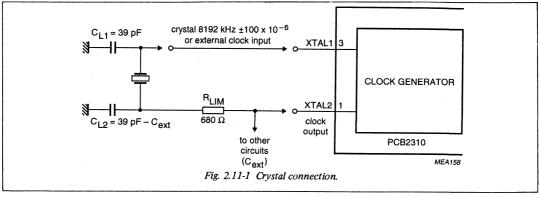

- 3 XTAL1 Inverting buffer input. The other side of the crystal is connected to pin 3. An 8192 kHz ± 100 ppm crystal must be used. An external clock generator can also be connected to this pin.

- 4 PO

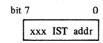

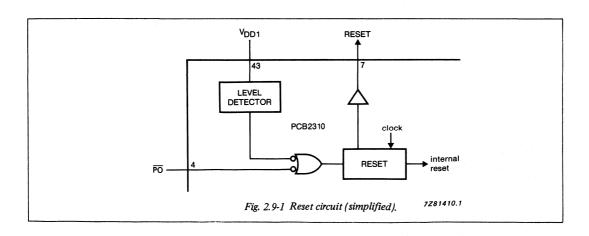

Power On/reset active LOW\* input. If there is a LOW pulse of > 1 μs, while the clock is running, the PCB2310 will be reset. If pin 4 is HIGH it will be automatically reset by an internal circuit provided the voltage on VDD1 (pin 43) is < 1,2 V and rising to 5 V with a slope > 5 V/ms.

- 5 COMP Compensation active LOW output.

6 COMP Compensation active HIGH output.

These two outputs are used to compensate the change in inductive current in the transformer (Fig. 4.0-3).

- 7 RESET Active HIGH output. If RESET = HIGH

the PCB2310 is performing an internal reset.

Pin 7 could also be used to reset the

microcontroller. After power up this pin

will be HIGH for 1 ms.

- 8 VSL Subscriber line connection input.

VSL = HIGH indicates that the PCB2310 is part of a gateway to other network(s) such as ISDN 'S reference point'.

- 9 THSL Terminal highway slave mode selection input.

THSL = LOW puts the Terminal Highway

(THW) interface to the normal master mode.

THSL = HIGH switches the PCB2310 to the slave mode on the Terminal Highway. In this mode THCL (pin 37) and THSC (pin 35) are external inputs.

- 10 MCO

Master clock output (4096 kHz). This output can be used as a clock output to drive peripheral circuits. The output is the crystal frequency divided by 2 with a duty cycle of 50%.

- 11 RX2 THW time slot assignment output.

RX2 = HIGH during time slot on the THW that is set by the command <SBS> (see section 2.7.5).

- 12 TSA/

SLDEN

Input signal to select between time slot assignment and SLD bus signals. If

TSA = LOW pins SIP (pin 16)

and MM (pin 13) are in the SLD mode. If

TSA = HIGH these pins are switched to Time

Slot Assignment mode.

- 13 RX1/MM THW time slot assignment output/Master Mode selection input. If TSA = HIGH, this pin is an output, and the signal is HIGH during the time slot on the THW that is set by the command <SBS>.

If in the SLD mode (TSA = LOW) this is an input pin and selects between the master mode or the slave mode on the SLD bus:

MM = HIGH = Master mode;

MM = LOW = Slave mode.

14 ESC/

SDIR

SDIR

SDIR

SUBSET STATES SUBSET STATES SUBSET SUBS

PCB2310 is master on the IST bus.

15 SCLK

SLD clock input/output.

If master on the SLD bus (TSA = LOW;

MM = HIGH) SLCK provides the 512 kHz

clock signal, if slave (TSA = LOW;

MM = LOW) the 512 kHz clock is input

to this pin.

<sup>\*</sup> LOW means voltage on pin 4 is equal to V<sub>SS</sub> (pin 22). HIGH means voltage on pin 4 is equal to V<sub>DD2</sub> (pin 44).

# 1.3 Signal description (continued)

| 16                     | TX1/<br>SIP | THW time slot assignment output/SLD data I/O** pin. If TSA = HIGH this pin is an output, and the signal is HIGH during the time slot on the THW that is set by the                                                                                                                                                                                    | 32 | ALE              | Address latch enable input. A HIGH on this pin latches the data on the DB7-0 I/O port into the address latch provided $\overline{\text{CE}}$ (pin 33) is LOW.                                                                                                            |

|------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |             | command <sbs>.</sbs>                                                                                                                                                                                                                                                                                                                                  | 33 | CE               | Chip enable active LOW input.                                                                                                                                                                                                                                            |

|                        |             | If slave on the SLD bus (TSA = LOW;<br>MM = LOW) data can be transmitted in the<br>B <sub>1</sub> and B <sub>2</sub> channels when SDIR (pin 14) is<br>LOW and in the other channels when the                                                                                                                                                         | 34 | ISTOUT2          | IST bus output pin. 3-state output, capable of directly driving the IST bus. Complementary to ISTOUT1 (pin 40).                                                                                                                                                          |

|                        |             | output is 3-state.  Both B <sub>1</sub> and/or B <sub>2</sub> channels can be programmed to output a high impedance.                                                                                                                                                                                                                                  | 35 | THSC             | Terminal highway synchronization input/output. When THW interface is in master mode (THSL = LOW) pin 35 outputs                                                                                                                                                          |

|                        |             | If master on the SLD bus (TSA = LOW; MM = HIGH) the B <sub>1</sub> , B <sub>2</sub> , S and C channels are transmitted when ESC is HIGH. Data is put on the SIP output at a positive transition of SCLK. The idle code in the B <sub>1</sub> , B <sub>2</sub> and C channels is all logic 1's and in the S channel the initial code is all logic 0's. |    |                  | a pulse with a duration of one 2048 kHz cycle and a repetition frequency of 8 kHz. When THW interface is in slave mode (THSL = HIGH) pin 35 becomes an input. If monitor mode is selected (see section 2.10), pin 35 outputs a strobe to monitor the bd receive channel. |

| 17                     | TX2         | THW time slot assignment output. TX2 is HIGH during the time slot on the THW that is set by the command <sbs>.</sbs>                                                                                                                                                                                                                                  | 36 | THDA             | Terminal highway data I/O** pin. Data is put on this line on a positive transition of THCL (pin 37).                                                                                                                                                                     |

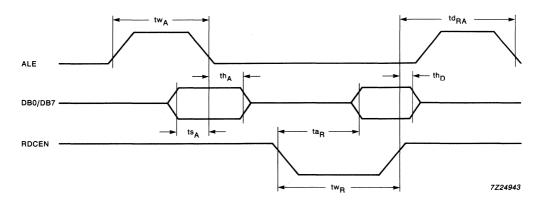

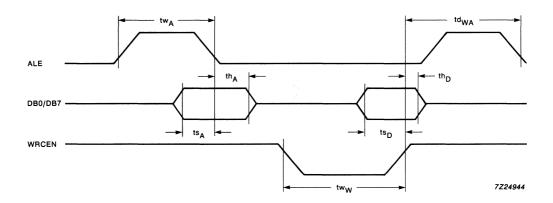

| 18-<br>20<br>23-<br>27 | DB7-0       | Combined address input and data I/O port. These pins are used to access internal registers P80 to P83. The selection between address and data is made by ALE (pin 32).  WR (pin 31) and RD (pin 30) will select input or output respectively.                                                                                                         | 37 | THCL             | Terminal highway clock input/output pin. This output can drive 4 TTL (= 16 LSTTL) inputs. When THW interface is in master mode this pin provides a 2048 kHz clock. When THW interface is in slave mode this pin is the input for a 2048 kHz clock.                       |

| 21                     | n.c.        | not connected.                                                                                                                                                                                                                                                                                                                                        | 38 | TEST1            | These pins are for production test and both                                                                                                                                                                                                                              |

| 22                     | VSS         | Ground.                                                                                                                                                                                                                                                                                                                                               | 39 | TEST2            | must be LOW for normal operation.                                                                                                                                                                                                                                        |

|                        | n.c.        | not connected.                                                                                                                                                                                                                                                                                                                                        | 40 | ISTOUT1          | IST bus output pin. 3-state output, capable                                                                                                                                                                                                                              |

|                        | IREQ        | Interrupt request is an open drain output.                                                                                                                                                                                                                                                                                                            |    |                  | of directly driving the IST bus. Complementary to ISTOUT2 (pin 34).                                                                                                                                                                                                      |

| 2)                     |             | This signal is active LOW. If a bit is set in the interrupt register P80, pin 29 is made LOW.  If the interrupt is serviced by reading register P80 the interrupt will be reset.                                                                                                                                                                      | 41 | ISTIN            | IST bus input pin (input of the IST bus receiver, see section 2.3 and IST bus specification).                                                                                                                                                                            |

| 30                     |             | Read active LOW input. If this input is LOW data from the addressed register will be put                                                                                                                                                                                                                                                              |    | ISTREF           | IST bus reference pin. This pin outputs a voltage of V <sub>DD2</sub> /2 ± 60 mV.                                                                                                                                                                                        |

| 21                     | 1775        | on the DB7-0 I/O port.                                                                                                                                                                                                                                                                                                                                | 43 | $v_{DD1}$        | Supply voltage for the analogue parts of the PCB2310. $V_{DD1} - V_{SS} = 5 \text{ V} \pm 5\%$ .                                                                                                                                                                         |

| 31                     |             | Write active LOW input. If this input is LOW data on the DR7-01/O port will be written                                                                                                                                                                                                                                                                | 44 | V <sub>DD2</sub> | Supply voltage for the digital parts of the                                                                                                                                                                                                                              |

$44\ V_{DD2}$

Supply voltage for the digital parts of the PCB2310.  $V_{DD2}-V_{SS}$  = 5 V  $\pm$  5%.

into the addressed register.

data on the DB7-0 I/O port will be written

<sup>\*\*</sup> I/O indicates a 3-state pin; HIGH, LOW or high impedance.

#### 2.0 FUNCTIONAL DESCRIPTION

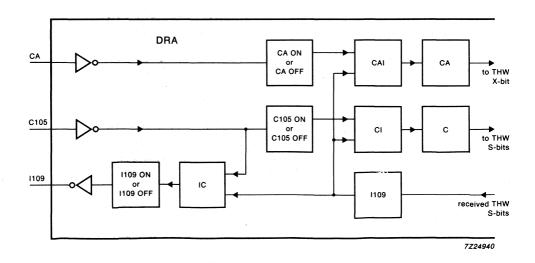

#### 2.1 General description

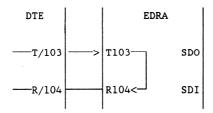

The PCB2310 performs the electrical interface and the protocols on the IST bus as described in the IST bus specification. A brief description of the IST bus is given in section 2.2.

The circuit-switched channels on the IST bus (b1 to b8) are mapped on specific Terminal Highway (THW) time slots and can be routed to SLD B<sub>1</sub> and B<sub>2</sub> channels and vice versa.

$$IST b1 to b8 < \underbrace{FIXED}_{\begin{subarray}{c} MAPPING\\ \end{subarray}} THW < \underbrace{CONTROLLABLE}_{\begin{subarray}{c} ALLOCATION\\ \end{subarray}} SLD (B_1, B_2)$$

The packet-switched bd channel on the IST bus is routed through layer 1 and layer 2 entity. The service access point on the layer 2 service is performed by the microcontroller I/O port.

The microcontroller I/O port performs the interface for the control stages of the PCB2310 and is also the access point for the C and S channels on the SLD bus.

An on-chip reset circuit and clock generator minimizes the number of external components.

#### 2.2 IST bus description

The PCB2310 is fully developed to operate according to the IST bus specification. The PCB2310 can be connected direct to the IST bus via a transformer.

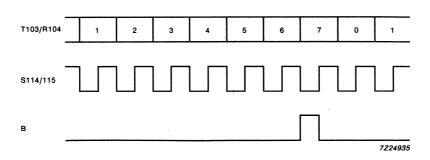

The 8 kHz (125  $\mu$ s) synchronous IST bus frame contains ten time division multiplexed channels as shown in Fig. 2.2-1:

- 1 x 5-bit synchronization channel; Frame (F)

- 1 x 64 kbit/s packet-switched channel; Data (bd)

- 8 x 64 kbit/s circuit-switched channels; Data/voice (b1 to b8)

Each channel is preceded with an 'occupied' bit which is logic 1 if the channel is occupied.

#### 2.2.1 bd channel

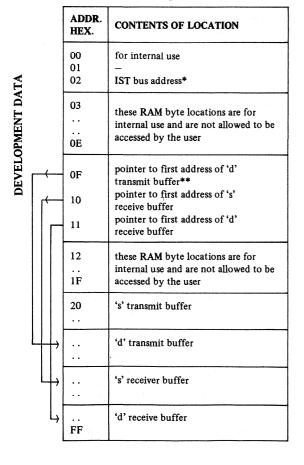

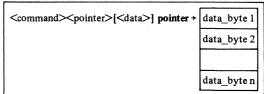

The PCB2310 interfaces the bd channel with the 8-bit microcontroller I/O port, for which it performs a full layer 1 and 2 service as defined in the IST bus specification. It performs all the requirements for error detection and correction by re-transmissions and flow control on the packets transmitted in the bd channel. Layer 2 packets for re-transmission can be stored in the  $256 \times 8$  internal RAM.

#### 2.2.2 b channels

The PCB2310 also handles the circuit-switched channel connections; the access mechanism being completely distributed. There is no network manager. Command <FFC> (see Table 2.6-6) orders the PCB2310 to access a free b1 to b8 circuit-switched channel. A b1 to b8 channel is fetched by transmitting an 'occupied' bit (see Fig. 2.2-1) and the data on the corresponding THW time slot will be mapped upon this IST bus b1 to b8 channel. With command <OAR> the ordered channel will be occupied as soon as it is released.

A channel is seen free if the 'occupied' bit of that channel is logic 0 for at least two consecutive frames.

A channel is seen released if the 'occupied' bit is logic 0 for at least one frame.

#### 2.2.3 Frame channel

The PCB2310 can operate on the IST bus in two modes; master or slave. In the PCB2310 the complete distributed nester/slave arbitration protocol is implemented (see IST bus specification). All IST slaves will synchronize on the frame channel as transmitted by the IST master. If VSL (pin 8) is HIGH and the PCB2310 is master on the IST bus,

the PCB2310 will synchronize on the 8 kHz external input signal at ESC/SDIR (pin 14).

The PCB2310 also performs some maintenance functions such as IST BUS\_DOWN and IST BUS\_UP.

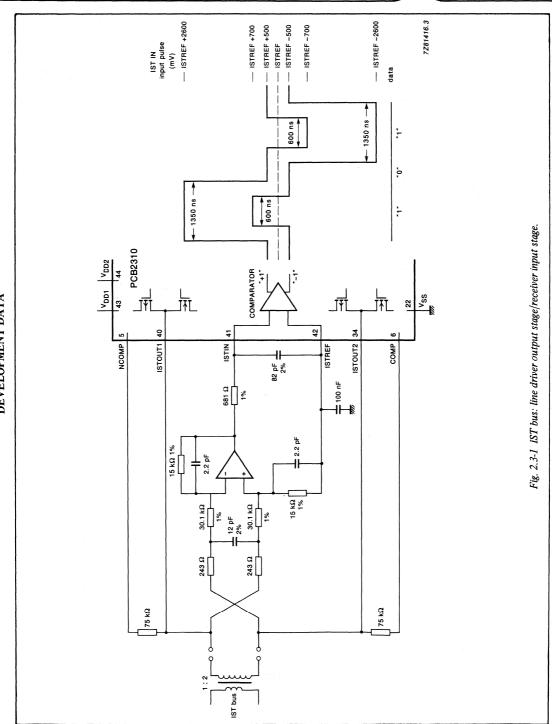

## 2.3 IST bus I/O stage

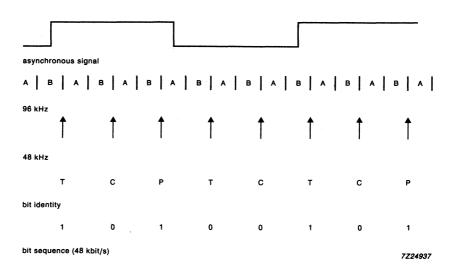

The IST bus I/O stage consists of a receiver and a transmitter. The line code is Alternative Mark Inversion (AMI).

The bit rate is 1024 kbit/s based on an 8192 kHz crystal. ISTOUT1 (pin 40) and ISTOUT2 (pin 34) drive the IST bus while ISTREF (pin 42) is held at  $V_{DD}/2 \pm 60$  mV. To buffer ISTREF an external 100 nF capacitor should be connected between pin 42 and  $V_{SS}$ . To handle the IST bus specification a transformer with a ratio — IST bus: PCB2310 = 1:2 is required.

ISTIN (pin 41) is the input for the receiver comparator. The comparator reference voltage is derived from the voltage on pin 42. There is hysteresis built in to the comparator. The comparator can handle input pulse limits as defined in Fig. 2.3-1.

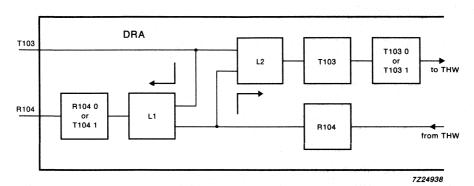

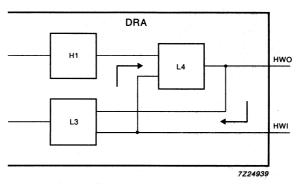

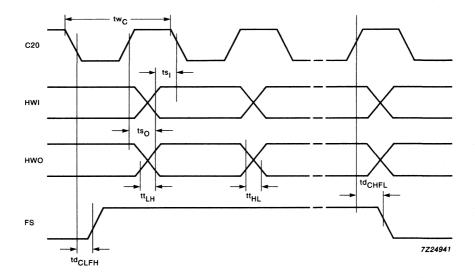

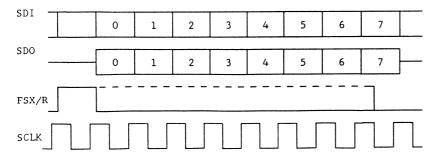

#### 2.4 Terminal highway interface

The Terminal Highway (THW) is a 2 Mbit/s three-wire full duplex PCM highway for 64 kbit/s circuit-switched channels. The THW will normally be used to interconnect a PCM codec filter or a data terminal that transmits in one of the IST b1 to b8 channels.

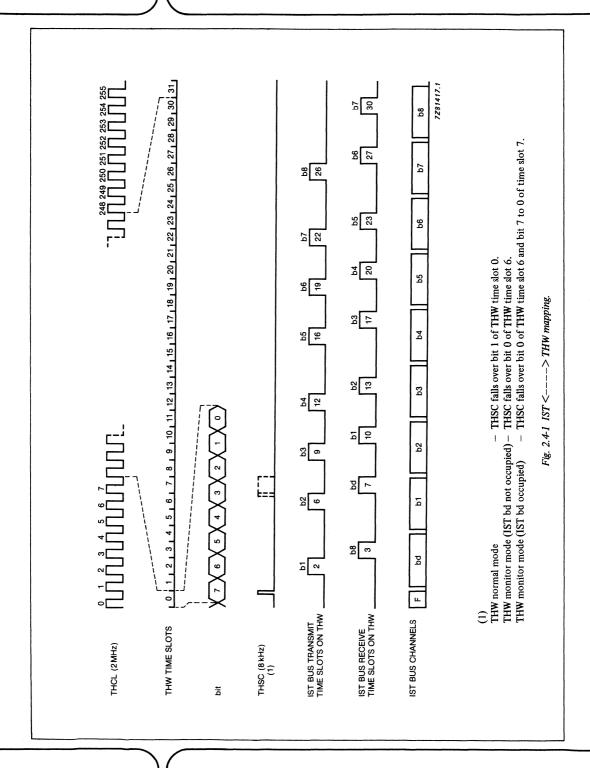

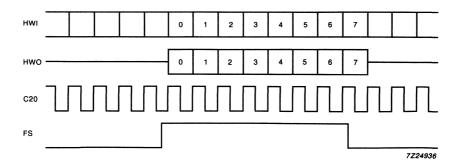

The THW offers 32 time slots, 17 of which are used to transmit and receive the IST bus channels. Channels b1 to b8 and bd are mapped upon fixed time slots on the THW (see Fig. 2.4-1). The remaining 14 time slots are 'free'. The THDA data is clocked with the 2048 kHz clock. However, time slots 0 and 31 may be temporarily clocked with a clock period that varies by 25% for synchronization.

The THW interface can operate in 3 separate modes:

- Master

- Slave

- Monitor